## Beschreibung der Einzelbaugruppen

### 3.2.1 Treiber für Adress-, Daten- und Steuerbus

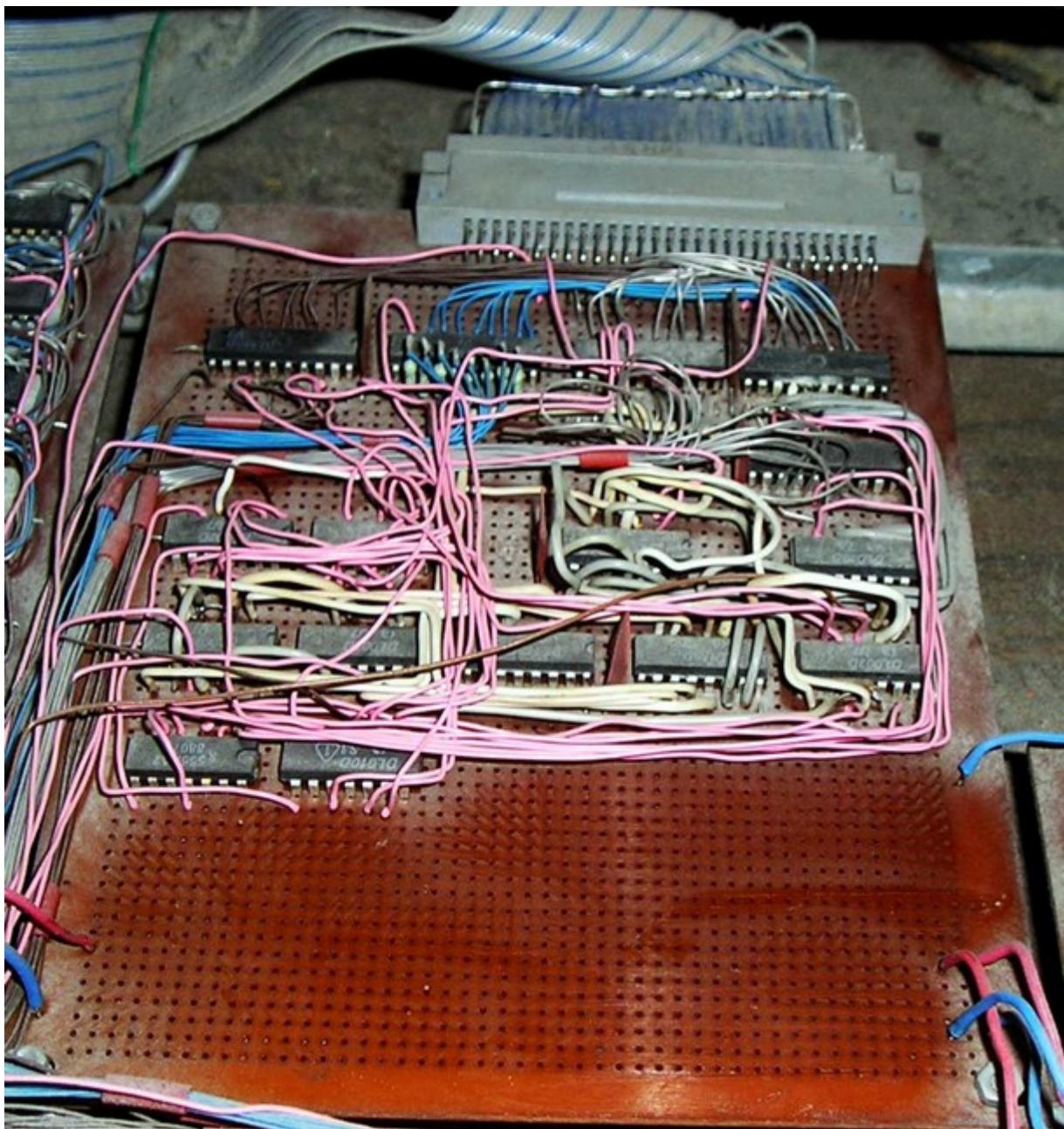

Der Adress-, Daten- und Steuerbus im KC85/3 ist ungetrieben, d.h. die zulässige Belastung (Lastfaktoren) richtet sich nach der CPU U880D, also nicht mehr als eine TTL-Lasteinheit. In der Dokumentation zum M005 wird von MPM sogar nur eine LS-Lasteinheit vorgeschrieben. Daraus resultiert, daß für alle Erweiterungen über das Expansions-Interface entsprechende Treiber vorzusehen sind.

Für den niederwertigen Teil des Adressbus (A0 – A7) wird das 2x mit invertierenden Bustreibern D1 und D2 realisiert, so daß damit gleichzeitig die für Decodierungszwecke notwendigen invertierten Adress-Signale (/A0 - /A7) bereitstehen.

Für den höherwertigen Teil des Adressbusses (A8 – A15) wird das mit dem nichtinvertierenden Treiber D3 realisiert.

Etwas komplizierter ist die Realisierung des Datenbus-Treibers. Hierbei ist die Datenrichtung zu berücksichtigen, d.h. Datenfluß vom KC zum SEW oder umgekehrt. Mit einer einfachen ODER-Verknüpfung der CPU-Steuersignale RD und M1 ist das unter bestimmten Bedingungen leicht möglich.

Damit es zu keinen Datenbus-Konflikten im KC kommt, deren Folge im unkritischstem Fall Funktionsverlust oder Programmabsturz sind, müssen entsprechende Vorkehrungen getroffen werden, insbesondere für den Fall der Datenflußrichtung zum KC.

Der bidirektionale Datenbustreiber D4 wird in Grundrichtung SEW -> KC betrieben, mit seinen TriState-Ausgängen ist er jedoch nur dann aktiviert, wenn:

- keine I/O-Adresse 80H anlegt,

- die Geräteadresse im Bereich von 10H – 8FH liegt und

- kein interner Tastatur-Interrupt anlegt.

Außerdem muß es von Seiten der CPU (KC) möglich sein, einen Interrupt-Vektor von einem der U880-Systemschaltkreise, die für I/O-Aufgaben eingesetzt sind, lesen zu können.

Die sich ergebende Logik-Schaltung zur /OE-Freigabe des Datenbustreibers D4 scheint auf den ersten Blick recht kompliziert zu sein und ist vielleicht hinsichtlich der Signallaufzeit auch nicht optimiert, aber auf Grund der geringen Taktfrequenz des KC ausreichend.

Damit der interne Datenbus im SEW bei Deaktivierung von D4 keine undefinierten Zustände annimmt, werden die einzelnen Datenbus-Leitungen über die Pullup-Widerstände R1 – R8 "hochgelegt". Dies ist insbesondere für die Bildung der so genannten Strukturbytes der einzelnen Module von Bedeutung, denn diese werden mit einfachen Open-Kollektor-Gattern realisiert. (siehe ab Pkt. 3.3).

Der Steuerbus wird ebenfalls mit einem invertierenden Treiber D5 realisiert, so daß die Steuerbus-Signale gleich in der verarbeitungsmäßig günstigeren Form als Positiv-Logik vorliegen.