# **Graphic-LCD am AVR**

Dipl.-Ing. (FH) Peter Salomon

© Copyright by Peter Salomon, Berlin – erarbeitet 2013 (2018)

Die vorliegende Publikation ist urheberrechtlich geschützt. Alle Rechte, Irrtum und Änderungen vorbehalten. Eine auch auszugsweise Vervielfältigung bedarf in jedem Fall der Genehmigung des Herausgebers. Die hier wiedergegebenen Informationen, Dokumente, Schaltungen, Verfahren und Programmmaterialien wurden sorgfältig erarbeitet, sind jedoch ohne Rücksicht auf die Patentlage zu sehen, sowie mit keinerlei Verpflichtungen, noch juristischer Verantwortung oder Garantie in irgendeiner Art verbunden. Folglich ist jegliche Haftung ausgeschlossen, die in irgendeiner Art aus der Benutzung dieses Materials oder Teilen davon entstehen könnte.

Für Mitteilung eventueller Fehler ist der Autor jederzeit dankbar. Es wird darauf hingewiesen, dass die erwähnten Firmen- und Markennamen, sowie Produktbezeichnungen in der Regel gesetzlichem Schutz unterliegen.

# **Inhaltsverzeichnis**

6.7.1

6.8.

6.9.

6.9.1

6.8.1.

<u>Test</u>

<u>Test</u>

UP GLCD\_txt

GLCD\_write - Routine

Allgemeines zu "Text"

|          | <u> </u>                                 |

|----------|------------------------------------------|

| 1.       | <u>Vorbemerkungen</u>                    |

| 2.       | <u>Produkt-Informationen</u>             |

| 2.1.     | Preiswertes GLCD mit T6963-Controller    |

| 2.2.     | Preiswertes GLCD mit KS0108-Controller   |

| 3.       | Hardware-Vorrausetzungen                 |

| 4.       | <u>Hardware - Initialisierung</u>        |

| 4.1.     | Variante mit T6963-Controller            |

| 4.2.     | Variante mit KS0108-Controller           |

| 5.       | Befehlsliste des KS0180                  |

| 6.       | Grund-Funktionen                         |

| 6.1.1.   | GLCD_init - Routine                      |

| 6.1.1.   | Test UP GLCD_init                        |

| 6.1.1.1. | Test mit dem DRAGON-Board                |

| 6.1.1.2. | Test mit dem Original JTAGICEmkII        |

| 6.2.     | GLCD_ON - Routine                        |

| 6.2.1.   | Test UP GLCD_on                          |

| 6.2.1.1. | Alternative Test-Instrumentarien         |

| 6.2.1.2. | Test mit JTAGICEmkII                     |

| 6.3.     | GLCD_CLR - Routine                       |

| 6.3.1.   | Testergebnis GLCD_clr                    |

| 6.3.2.   | Schlussfolgerungen zur Weiterentwicklung |

| 6.3.2.1. | <u>Flussdiagramm</u>                     |

| 6.4.     | Struktur des Display-RAMs                |

| 6.5.     | GLCD_SetX - Routine                      |

| 6.5.1    | <u>Test</u>                              |

| 6.6.     | GLCD_SetY - Routine                      |

| 6.6.1    | <u>Test</u>                              |

| 6.7.     | GLCD_read - Routine                      |

| 6.9.2    | <u>Zeichentabelle</u>                  |

|----------|----------------------------------------|

| 6.9.3    | Übertragung der Tabellenwerte          |

| 6.9.4.   | <u>Test</u>                            |

| 6.10     | <u>Linie</u>                           |

| 6.10.1   | Allgemeines zur Linie                  |

| 6.10.2   | Line - Vorbereitende Maßnahmen         |

| 6.10.3   | UP GLCD_LineH                          |

| 6.10.3.1 | Test GLCD_LineH                        |

| 6.10.4   | UP GLCD_LineV                          |

| 6.10.4.1 | Programmtechnische Realisierung Fall 1 |

| 6.10.4.2 | Programmtechnische Realisierung Fall 2 |

|          | XXX                                    |

# 1. Vorbemerkungen

Im Gegensatz zu einfachen LCDs zur Darstellung von ausschließlich Zeichen (Buchstaben, Zahlen, Sonderzeichen) mit 1, 2 oder 4 Zeilen und max. 20 Zeichen gibt es bei Graphic-LCDs die unterschiedlichsten Bauformen und damit Auflösungen in horizontaler und vertikaler Dimension. Hinzu kommt noch, daß es zwar einige quasi-Standard-Controller gibt, z.B.

T6863.pdf

HD61202.pdf,

KS0108b.pdf,

ST7565R.pdf

darüber hinaus aber noch jede Menge exotische Spezial-Controller, auch für ausgefallene Pixel-Anzahl in horizontaler und vertikaler Richtung.

## 2. Produkt-Informationen

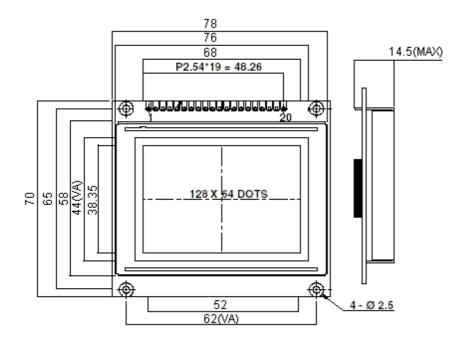

# 2.1. Preiswertes GLCD mit T6963-Controller (\$22,90)

(http://www.futurlec.com/LED/LCD128X64.shtml)

## **Features**

►Built-in Controller (T6963C)

►+5V Power Supply

►1/64 Duty Cycle

►Built-in Backlight

Module Abmessung 78 x 70 x 12 mm

Bildgrösse 65 x 44 mm

Pixel Grösse 0,39 x 0,55 mm

Pixel Abstand 0,44 x 0,6 mm

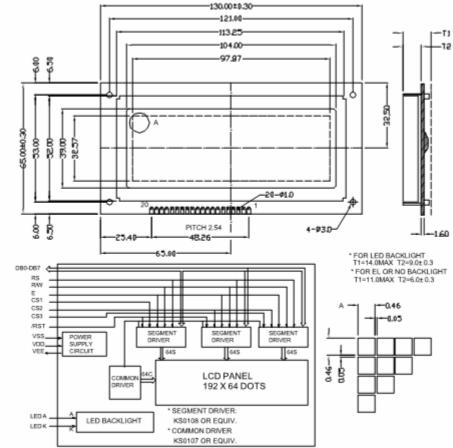

# **2.2. Preiswertes GLCD mit KS0108-Controller** (6,95 Euro)

(http://www.pollin.de/shop/dt/NzgyOTc4OTk-

/Bauelemente Bauteile/Aktive Bauelemente/Optoelektronik/LCD Modul DM19264A 02 192x64

Pixel.html)

Grafisches LCD mit gelber LED-Hintergrundbeleuchtung und integriertem Controller (KS0108B).

#### Technische Daten:

- Betriebsspannung 5 V-

- 192x64 Pixel

- integrierter Controller KS0108B

- LED-Hintergrundbeleuchtung

- 20-poliger Anschluss

- sichtbarer Bereich 104x39 mm

- Außenmaße (LxBxH): 130x65x12,5 mm

All dimensions in mm. Tolerance +0\_3mm unless otherwise specified.

Die Kontrastspannung an Pin 3 wird mittels Poti eingestellt – angeschlossen zwischen Pin 19 (-5V/-10V) und Vdd (Pin 2). Es ist möglich, daß Pin 19 nicht angeschlossen ist (Leiterbahnunterbrechung), ggf. reichen die -5V mit einem integrierten 7660 nicht aus, dann kann ein zweiter nachgerüstet werden, um -10V zu erhalten. Die CSx-Signale sind LOW-aktiv. Mit der fallenden Flanke von E werden die Daten übernommen, d.h. die Daten müssen auch nach der fallenden Flanke von E noch stabil anliegen.

Bei diesem Pollin-Sonderangebot fehlt die Verbindung zwischen dem Anschluß-Pin 19 und Pin 5 des 7660, d.h. die -5V liegen nicht am Anschluß 19 an. Diese Verbindung muß nachträglich hergestellt werden, wenn mit dem internen -5/-10V-Generator gearbeitet werden soll.

Die Anschlüsse der Beleuchtungs-LEDs sind separat seitlich herausgeführt. Nach Datenblatt sollen hier 4,2V anliegen, wobei  $I_{LED} < 300 \text{mA}$  sein muß, was mit einem Vorwiderstand von 4,7 Ohm, geschaltet von der +5V-Betriebsspannung realisierbar ist.

# 3. Hardware-Vorrausetzungen

Vergleich der Anschaltung:

| KNr | Chr-LCD      | GLCD (T6963) | GLCD (KS0108)          |

|-----|--------------|--------------|------------------------|

| 1   | GND          | FG/Vee (0V)  | Vss - GND              |

| 2   | Vcc          | Vss (0V)     | Vdd - +5V              |

| 3   | LCD-Kontrast | Vdd (+5V)    | Vo (Vdd-15VVdd+0,3V)   |

| 4   | RS           | Vo (0 10V)   | RS                     |

| 5   | RW           | WR           | R/W                    |

| 6   | E            | RD           | Е                      |

| 7   | DB0 (GND)    | CE           | DB0                    |

| 8   | DB1 /GND)    | C/D          | DB1                    |

| 9   | DB2 (GND)    | Reset        | DB2                    |

| 10  | DB3 (GND)    | DB0          | DB3                    |

| 11  | DB4          | DB1          | DB4                    |

| 12  | DB5          | DB2          | DB5                    |

| 13  | DB6          | DB3          | DB6                    |

| 14  | DB7          | DB4          | DB7                    |

| 15  | NC           | DB5          | CS1                    |

| 16  | NC           | DB6          | /RST                   |

| 17  |              | DB7          | CS2                    |

| 18  |              | FS           | CS3                    |

| 19  |              | K (LED +5V)  | VEE (neg. Outp5V/-10V) |

| 20  |              | A (LED 0V)   | A (LED-Backlight 4,2V) |

# 4. Hardware - Initialisierung

# 4.1. Variante mit T6963-Controller

Bevor irgendwelche Aktionen mit dem GrController unternommen werden können, muß dieser (wie auch die CharController) initialisiert werden. In der *ApplicationNote.pdf* wird dazu folgendes geschrieben:

Zunächst muß das GrLCD incl. Controller nach dem Zuschalten von Vcc mindestens für 6 Takte (oder 1ms) an /RES auf LOW (Reset) gehalten werden. Das kann mittels 10kOhm gegen Vcc und 0,1µF gegen Masse erreicht werden (siehe Appl.-Schaltung S7 der *ApplicationNote.pdf*).

Da Steuer-Controller (AVR) und GrController asynchron arbeiten, muß bevor

irgendwelche Befehle oder Daten an den GrController gesendet werden, der Statuszustand von GrController geprüft werden.

In Anlehnung an T6963c\_main\_v1.asm bzw. TEST2 - T6963.ASM wird die Initialisierungs-Routine so aussehen:

(weiteres wird zunächst ausgesetzt, wegen Orientierung auf das KS0180-Controller-Display)

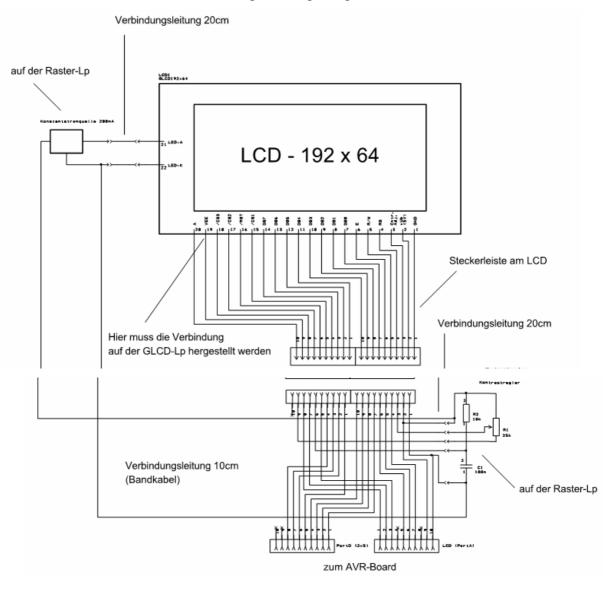

## 4.2. Variante mit KS0108-Controller

Ein Test ist erst nach der Hardware-Implementierung möglich.

Dazu wird zunächst eine Anschaltung wie folgt vorgenommen:

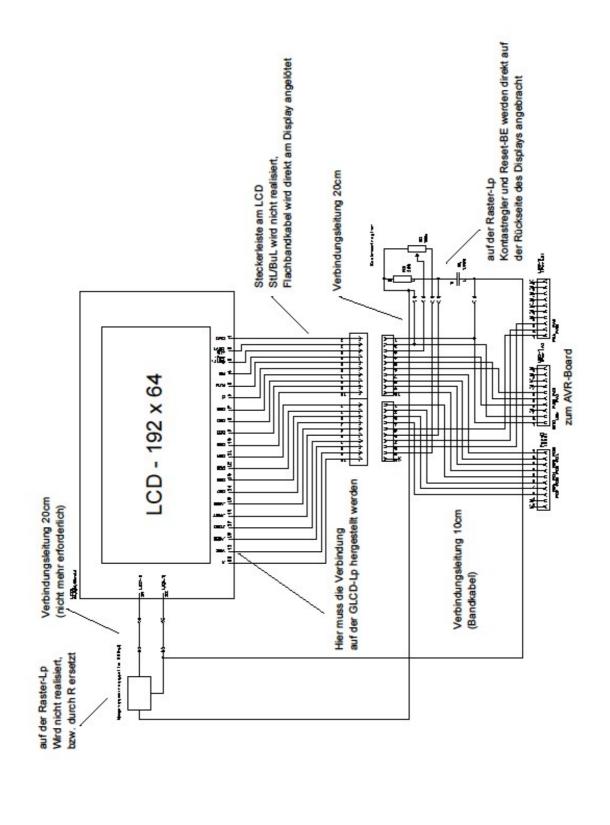

Die Anschaltung wurde noch mal korrigiert:

Das Daten-Interface wird adaptiert in Anlehnung an die Originalschaltung des "ATMegaEvoBoard" wie folgt:

| Pin 4 (RS)    | ->                                                                                                                                                   | PortA0                                                                                                                                                                                   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 5 (R/W)   | ->                                                                                                                                                   | PortA1                                                                                                                                                                                   |

| Pin 6 (E)     | ->                                                                                                                                                   | PortA2                                                                                                                                                                                   |

| Pin 12 (/CS0) | ->                                                                                                                                                   | PortA5                                                                                                                                                                                   |

| Pin 13 (/CS1) | ->                                                                                                                                                   | PortA6                                                                                                                                                                                   |

| Pin 14 (/CS2) | ->                                                                                                                                                   | PortA7                                                                                                                                                                                   |

|               |                                                                                                                                                      |                                                                                                                                                                                          |

| Pin 1 (DB0)   | ->                                                                                                                                                   | PortD0                                                                                                                                                                                   |

| Pin 2 (DB1)   | ->                                                                                                                                                   | PortD1                                                                                                                                                                                   |

| Pin 3 (DB2)   | ->                                                                                                                                                   | PortD2                                                                                                                                                                                   |

| Pin 4 (DB3)   | ->                                                                                                                                                   | PortD3                                                                                                                                                                                   |

| Pin 5 (DB4)   | ->                                                                                                                                                   | PortD4                                                                                                                                                                                   |

| Pin 6 (DB5)   | ->                                                                                                                                                   | PortD5                                                                                                                                                                                   |

| Pin 7 (DB6)   | ->                                                                                                                                                   | PortD6                                                                                                                                                                                   |

| Pin 8 (DB7)   | ->                                                                                                                                                   | PortD7                                                                                                                                                                                   |

|               | Pin 5 (R/W) Pin 6 (E) Pin 12 (/CS0) Pin 13 (/CS1) Pin 14 (/CS2)  Pin 1 (DB0) Pin 2 (DB1) Pin 3 (DB2) Pin 4 (DB3) Pin 5 (DB4) Pin 6 (DB5) Pin 7 (DB6) | Pin 5 (R/W) -> Pin 6 (E) -> Pin 12 (/CS0) -> Pin 13 (/CS1) -> Pin 14 (/CS2) ->  Pin 1 (DB0) -> Pin 2 (DB1) -> Pin 3 (DB2) -> Pin 4 (DB3) -> Pin 5 (DB4) -> Pin 6 (DB5) -> Pin 7 (DB6) -> |

Sind die o.g. aufgeführten Hardware-mäßigen Verbindungen hergestellt, sollte zunächst die LED-Beleuchtung geprüft werden, des Weiteren die LCD-Kontrasteinstellung mittels Poti R1.

R2 in Verbindung mit C1 bewirkt ein Reset des GLCD beim Einschalten. Entsprechend der Zeitkonstante:

$$T=2\pi$$

\* R2 \* C1 = 6,28 \* 10<sup>4</sup> V/A \* 10<sup>-7</sup> As/V = 6,28 \* 10<sup>-3</sup> s bzw.  $\approx$  6ms ergibt sich, daß erst nach ca. 10ms an das GLCD Daten oder Befehlen gesendet werden können. Das ist bei der Init-Routine des AVR zu berücksichtigen.

Der Einschalt-Test erfolgte positiv, d.h. die Hintergrundbeleuchtung ließ sich ein- und ausschalten (ist im SP nicht enthalten).

Ansonsten bedarf es zunächst einige Test-Routinen, um auf dem Display etwas sehen zu können, siehe dazu Abschnitt 6 - <u>Grund-Funktionen</u>.

## 5. Befehlsliste des KS0180

Nach Datenblatt *KS0108b.pdf* und in Ergänzung zum Äquivalent-Chip *S6B0108-KS0108.pdf* von SAMSUNG sind folgende 7 Befehle verfügbar:

## (1) **DISPLAY ON/OFF**

Das Display ON/OFF-Flip-Flop schaltet die Flüssigkristall-Anzeige ON/OFF. Wenn das Flip-Flop zurückgesetzt wird (logisch), wird die Spannung an den Segment-Ausgängen selektiert oder nicht. Wenn das Flip-Flop gesetzt ist (logisch hoch), erscheint die nicht selektierte Spannung auf den Segment Ausgangsklemmen unabhängig von Display-RAM Daten. Der Status des Display ON/OFF-Flip-Flops kann geändert werden durch einen Befehl. Die Anzeige von Daten auf allen Segmenten verschwindet, während RSTB LOW ist. Der Status der Flip-Flop-Ausgang wird ausgegeben an DB5 vom Status Lesebefehl. Das Display ON/OFF-Flip-Flop wird vom CL-Signal synchronisiert.

RS R/W DB7 DB6 DB5 DB3 DB<sub>2</sub> DB1 DB<sub>0</sub> DB4 0 0 0 1 1 1 1 D 0 1

Die Daten-Anzeige wird aktiviert, wenn D=1 ist, und verschwindet, wenn D=0 ist. Obwohl die Daten nicht auf dem Bildschirm mit D=0, es bleiben die Daten im Anzeige-RAM. Daher können diese angezeigt werden, indem D=0 in D=1 geändert wird.

# (2) SetAdress (Y)

Y Adreßzähler bezeichnet die Adresse des internen Display Daten-RAMs. Eine Adresse wird vom Befehlssatz gesetzt und wird automatisch um 1 erhöht von Lese- oder Schreibvorgängen der Display-Daten.

RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 1 0 0 AC5 AC4 AC3 AC2 AC1 AC0

Y-Adresse (AC0 - AC5) des Daten-RAMs der Anzeige wird im Y-Adress-Zähler gesetzt. Eine Adresse wird durch den Befehlssatz gesetzt und um 1 automatisch nach jedem Lese- oder Schreibvorgänge von Display-Daten erhöht.

Die Bezeichnung der X-/Y-Adresse ist widersprüchlich. Der X-/Y-Bezeichnung zur Folge müssten die Datenbytes waagerecht in einer Zeile abgebildet werden und es demzufolge 8 Datenbytes auf einer Zeile bei 64 Zeilen untereinander geben. Die o.g. strukturelle Definition ist aus der "ApplNote - KS0108 (AN2147 - CYPRESS).pdf" entnommen worden – Ob aber ein Daten-Byte wirklich 8 Pixel senkrecht untereinander beschreibt, muß aber noch in der Realität überprüft werden.

## (3) **SetPage (X)**

Das X-Seiten Register bezeichnet die Seiten des internen Display Daten-RAMs. Eine Count-Funktion ist nicht verfügbar. Die Adresse wird gesetzt durch den Befehl:

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | 0   | 1   | 1   | 1   | AC2 | AC1 | AC0 |

X-Adresse (AC0 - AC2) des Displays-RAM wird im X-Adress-Register gesetzt. Schreiben oder Lesen von oder nach MPU wird in dieser angegebenen Seite ausgeführt, bis die nächste Seite gesetzt ist.

## (4) **Display StartLine**

Das Display-Startlinie-Register zeigt auf die oberste Zeile des Display-RAMs des LCDs. Die Bit-Daten (DB0 bis DB5) des Displays Startlinie werden im Anzeige-Startlinie-Register gehalten. Die gespeicherten Daten werden an den Z-Adreßzähler zur Voreinstellung des Z-Adress-Zählers übertragen, während FRM HIGH ist. Das wird angewendet zum Scrollen der verwendeten LCDs.

RS R/W DB7 DB6 DB5 DB3 DB2 DB1 DB4 DB<sub>0</sub> 1 1 AC4 AC3 AC2 AC1 0 0 AC5 AC<sub>0</sub>

Z-Adresse (AC0 - AC5) des Anzeige-Daten-RAMs wird im Anzeige-Startlinie-Register eingestellt und zeigt auf den Anfang des Bildschirms. Wenn das Anzeige-Tastverhältnis 1 / 64 oder andere (1 / 32 - 1 / 64) ist, werden die Daten der gesamten Zeilenanzahl des LCD-Bildschirm angezeigt, die von der Zeile der Display-Startlinie-Anweisung angegeben wurde.

## (5) Status Read

Dieser Befehl sollte vor allen Schreib- oder Leseaktionen ausgeführt werden, um z.B. sicherzustellen, daß der LCD-Controller bereits ist Daten zu empfangen, bzw. zu senden und nicht mit internen Operationen beschäftigt ist.

| RS | R/W | DB7  | DB6 | DB5    | DB4  | DB3 | DB2 | DB1 | DB0 |

|----|-----|------|-----|--------|------|-----|-----|-----|-----|

| 0  | 1   | BUSY | 0   | ON/OFF | RESE | Γ0  | 0   | 0   | 0   |

# · <u>BUSY</u>

Wenn BUSY = 1 ist, wird der Chip interne Operationen ausführen und keine Anweisungen akzeptieren.

Wenn BUSY = 0 ist, ist der Chip bereit alle Anweisungen zu akzeptieren.

#### · ON / OFF

Wenn ON / OFF = 1 ist das Display ausgeschaltet.

Wenn ON / OFF = 0 ist das Display eingeschaltet.

#### · RESET

Wenn RESET = 1 ist, wird das System initialisiert.

In diesem Zustand kann keine Anweisungen außer dem Status gelesen und akzeptiert werden.

Wenn RESET = 0 ist, ist die Initialisierung abgeschlossen und das System ist in den üblichen Betriebsbedingungen.

## (6) Write Display Data

Das Display-Daten-RAM speichert eine Anzeige für das LCD. Um einen Punkt der Matrix des LCDs anzuzeigen, ist ein Datenwert = 1 zu schreiben. Für den anderen Fall, den Aus-Zustand, schreibt man eine "0". Der Display-Daten-RAM-Adress- und Segment-Ausgang kann durch das ADC-Signal angesteuert werden.

- ADC = H ® Y-Adresse 0: S1 Y-Adresse 63: S64

- ADC = L ® Y-Adresse 0: S64 Y-Adresse 63: S1

ADC-Terminal ist zu verbinden mit VDD oder VSS (wird im GLCD nicht verwendet!).

Schreibt Daten (D0 - D7) in das Display-Daten-RAM. Nach dem Schreiben der Anweisung wird die Y-Adresse automatisch um 1 erhöht.

# (7) Read Display Data

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Liest Daten (D0 - D7) vom Display Daten-RAM. Nach der Lese-Instruktion wird die Y-Adresse automatisch um 1 erhöht.

# 6. Grund-Funktionen

Damit die Programmierung in übersichtlicher Weise erfolgen kann, sollen einige Grundfunktionen als modulare Routinen implementiert werden (Quellen-Vorgabe).

| GLCD_init | Init MCU-Interface          |

|-----------|-----------------------------|

| GLCD_res  | Reset the LCD               |

| GLCD_rdSt | Read current status of LCD  |

| GLCD_wrI  | Write an instruction to LCD |

| GLCD_rdD  | Read a data byte from LCD   |

| GLCD_wrD  | Write a data byte to LCD    |

|           |                             |

# Des weiteren

| GLCD_Busy   | Check if LCD is busy         |

|-------------|------------------------------|

| GLCD_Displ  | Check if LCD display is on   |

| GLCD_DisplI | Turn ON/OFF LCD display      |

| GLCD_SetY   | Set Y address of LCD         |

| GLCD_SetX   | Set X page of LCD            |

| GLCD_StL    | Set LCD display's start line |

# "Primitive" Graphic-Routinen

| GLCD_SetP  | Set a LCD-Pixel          |

|------------|--------------------------|

| GLCD_ClrP  | Clear a LCD-Pixel        |

| GLCD_LineA | Draw a general Line      |

| GLCD_LineH | Draw a horizontally Line |

| GLCD_LineV | Draw a vertical Line     |

| GLCD_Rect  | Draw a rectangle (H/V)   |

| GLCD_Circ  | Draw a circle            |

Im Laufe der Bearbeitung wird sich ergeben, daß von den o.g. Routinen einige anders strukturiert und ebenso auch anders benannt werden. Des Weiteren ist eine Text-Ausgabe notwendig. Der dazu notwenige Zeichen-Font wird in einer Tabelle fest im Programmcode verankert.

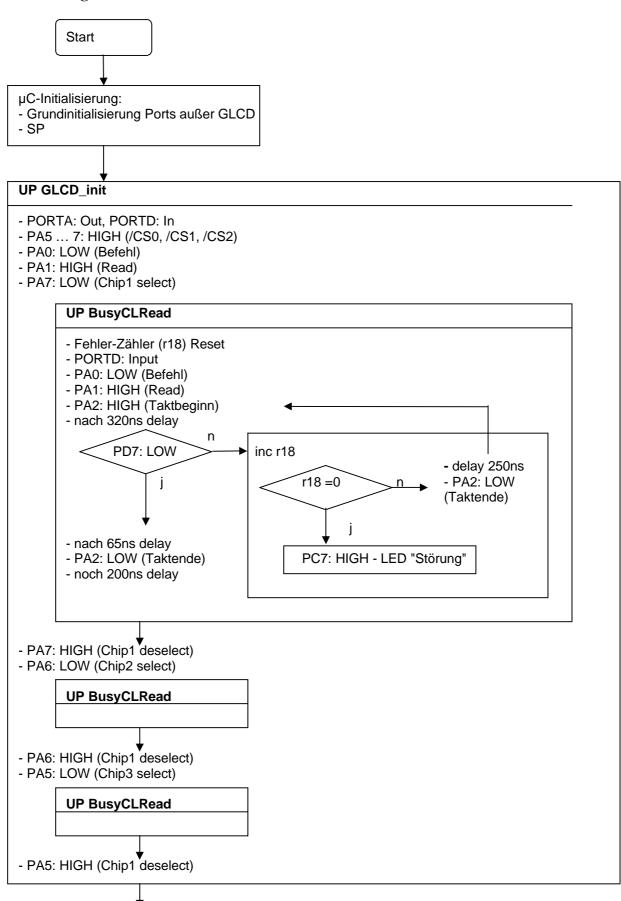

## 6.1. GLCD init - Routine

Für die Kommunikation mit dem Mikrocontroller müssen die von dem LCD genutzten Ports eine geeignete Anfangs-Initalisierung erhalten. Das betrifft:

```

PortA0 ->

Output (RS)

LOW (Befehle);

HIGH: Daten

->

PortA1 ->

Output (R/W)

HIGH (READ);

LOW: WRITE

->

PortA2 ->

LOW ->

Output (E)

->

HIGH -> LOW (CLOCK)

PortA5 ->

Output (/CS0)

HIGH

)

->

PortA6 ->

Output (/CS1)

) kein Chip ausgewählt

->

HIGH

PortA7 ->

Output (/CS2)

HIGH

)

->

PortD0 ->

Input (DB0)

PortD1 ->

Input (DB1)

PortD2 ->

Input (DB2)

PortD3 ->

Input (DB3)

PortD4 ->

Input (DB4)

PortD5 ->

Input (DB5)

PortD6 ->

Input (DB6)

PortD7 ->

Input (DB7)

```

Das ergibt folgende Code-Sequenz:

Die PORTD-Initialisierung ist eigentlich nicht notwendig, da diese beim MC-Start automatisch auf Input gesetzt wird.

Bevor irgendwelche Kommunikation mit dem LCD erfolgreich stattfinden kann, muß die Reset-Zeit der LCD-Controller abgewartet werden. Dazu kann pauschal eine Warte-Sequenz (ca. 10ms) eingefügt werden (siehe 4.2.), oder es wird das Busy-Flag der LCD-Controller ausgewertet. Damit könnte dann gleichzeitig die Betriebsbereitschaft des GLCDs festgestellt und ggf. mittels LED signalisiert werden (wobei hier vielleicht noch

die Betriebsbereitschaft anderer Komponenten mit berücksichtigt werden sollte) – ist hier (noch) nicht implementiert!

```

Init1: cbi PORTA, 5

sbic PORTD, 7

rjmp Init2

; setze PORTA5 (/CS0) auf LOW, Contr1 aktiviert

sbic PORTD, 7

; überspringe nächsten Befehl, wenn PD7 = LOW

rjmp Init2

; setze PORTA5 (/CS0) wieder auf HIGH, Contr1 deaktiv.

cbi PORTA, 6

; setze PORTA6 (/CS1) auf LOW, Contr2 aktiviert

sbic PORTD, 7

; überspringe nächsten Befehl, wenn PD7 = LOW

rjmp Init2

; bei HIGH = interne Op.

;

sbi PORTA, 6

cbi PORTA, 7

; setze PORTA6 (/CS1) wieder auf HIGH, Contr2 deaktiv.

cbi PORTA, 7

; setze PORTA7 (/CS2) auf LOW, Contr3 aktiviert

sbic PORTD, 7

; überspringe nächsten Befehl, wenn PD7 = LOW

rjmp init2

; bei HIGH = interne Op.

;

sbi PORTA, 7

rjmp weiter

;

Init2: rjmp init1

; wieder von vorn

```

Mit der Controller-Aktivierung durch /CSx wir <u>nicht</u> automatisch der Status gelesen und auf den Datenbus an PORTD ausgegeben. Hierzu ist RS auf LOW und R/W auf HIGH zu legen. Erst nach wenigstens 150ns darf der Enable- (Clock-) Impuls angelegt werden, d.h. E wird auf HIGH geschaltet und nach einer Wartezeit von mindestens 500ns wieder auf LOW zurückgesetzt. Erst dann liegt das Status-Byte auf dem Datenbus und demzufolge am PORTD an (siehe Datenblatt *KS0108b.pdf*).

Da die Prüf-Sequenz sbic PORTD, 7/rjmp Init2 mehrfach verwendet wird, kann diese und das E-Timing als UP ausgegliedert werden – vorausgesetzt RS und R/W sind vorher entsprechend o.g. gesetzt:

```

BusyCl: rcall delay150 sbi PORTA, 2 ; E \rightarrow HIGH rcall delay500 ; Impulsbreite cbi PORTA, 2 ; E \rightarrow LOW ; mit der H/L-Flanke wird das Statusbyte ; auf den Datenbus gelegt sbic PORTD, 7 ; überspringe nächsten Befehl, wenn PD7 = LOW rjmp BusyCl ; sonst bei HIGH = interne Op -> warten bis fertig ret

```

Dadurch vereinfacht sich Init1 und wird ergänzt mit:

```

Init1: cbi PORTA, 0

sbi PORTA, 1

cbi PORTA, 5

rcall BusyCl

; setze PORTA5 (/CS0) auf LOW

rcall BusyCl

; setze PORTA5 (/CS0) wieder auf HIGH

cbi PORTA, 6

; setze PORTA6 (/CS1) auf LOW

rcall BusyCl

;

sbi PORTA, 6

; setze PORTA6 (/CS1) wieder auf HIGH

cbi PORTA, 7

; setze PORTA7 (/CS2) auf LOW

rcall BusyCl

;

sbi PORTA, 7

; setze PORTA7 (/CS2) wieder auf HIGH

ret

; setze PORTA7 (/CS2) wieder auf HIGH

ret

; setze PORTA7 (/CS2) wieder auf HIGH

ret

; hier weiter

}

```

Diese Code-Sequenz ist als UP angelegt, so daß sie problemlos in das Gesamt-Programm integriert werden kann. Sollte die Initialisierung nicht erfolgreich verlaufen – Endlos-Schleife BusyCl -> rjmp busyCl - so könnte (sollte) das mit einer LED-Anzeige signalisiert werden – ist (noch nicht) implementiert!

Da die einzelnen Sequenzen der GLCD\_Init-Routine auch noch in anderen Routinen vorkommen können, wird hier noch weiter verallgemeinert, gleichzeitig erhalten die diesbezüglichen UPs entsprechende Namen:

```

(letzte gültige Version - Ausnahme BusyCl)

GLCD_init:

ldi R16, 0b11100111 ; PA0 – PA2, PA5 – PA7 -> Output

out DDRA, R16

ldi R16, 0b11100010 ;/CSO-/CS2 deaktiviert-

; W/R = HIGH, RS = LOW

out PORTA, R16

clr R16

; PD0 - PD7 -> Input

out DDRD, R16 rcall Commlon

; Kommunikation mit dem 1. Chip an

rcall commloff

; Kommunikation mit dem 1. Chip aus

; Kommunikation mit dem 2. Chip an

rcall Comm2on

rcall Comm2off

; Kommunikation mit dem 2. Chip aus

rcall Comm3on

; Kommunikation mit dem 3. Chip an

rcall Comm3off

; Kommunikation mit dem 3. Chip aus

; Rücksprung aus der Routine (Ende)

ret

cbi PORTA, 5

rcall BusyCl

; setze PORTA5 (/CS0) auf LOW

Commlon:

; Aufruf UP BusyCl

ret

```

```

Commloff:

sbi PORTA, 5

; setze PORTA5 (/CS0) wieder auf HIGH

ret

Comm2on:

cbi PORTA, 6

; setze PORTA6 (/CS1) auf LOW

rcall BusyCl

; Aufruf UP BusyCl

ret

; setze PORTA6 (/CS1) wieder auf HIGH

Comm2off: sbi PORTA, 6

ret

Comm3on:

cbi PORTA, 7

; setze PORTA7 (/CS2) auf LOW

rcall BusyCl

; Aufruf UP BusyCl

ret

; setze PORTA7 (/CS2) wieder auf HIGH

Comm3off: sbi PORTA, 7

ret

BusyCl:

rcall delay150

sbi PORTA, 2

; E → HIGH

rcall delay500

; Impulsanfang, Impulsbreite >500ns

; E → LOW, Impulsende

cbi PORTA, 2

; mit der H/L-Flanke wird das Statusbyte

; auf den Datenbus gelegt

sbic PIND, 7

; überspringe nächsten Befehl, wenn PD7 = LOW

; sonst bei HIGH = interne Op -> warten bis fertig

rjmp BusyCl

ret

; nachfolgende UPs werden z.Zt. nicht benötigt

; Zeitschleife ca. 150µs

delay150:

ldi R20, 255

ldi R21, 8

rcall time1

ret

delay500:

ldi R20, 255

; Zeitschleife ca. 500µs

ldi R21, 26

rcall time1

ret

time1:

dec R20

;Zeitschleifengenerator

brne time1

dec R21

brne time1

ret

```

Obwohl es so aussieht, als ob durch die vielen reall-Aufrufe der Code sehr aufgebläht wurde, können doch nun vorteilhaft im Weiteren die einzelnen UPs auch separat eingesetzt werden.

Im Erfolgsfall wäre als Nächstes der Befehl zum Einschalten des GLCDs zu geben.

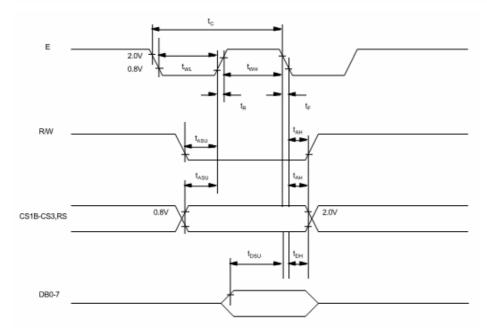

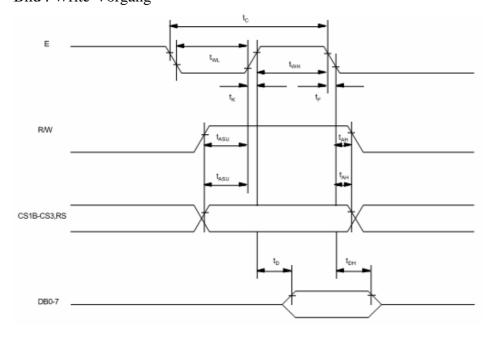

# BusyCL (Read) ist nicht korrekt! Siehe Timing...

In dem Dokument *KS0108.pdf* gibt es zwei Impulsdiagramme (2x Fig.3 - MPU write timing), die für die nachfolgenden Betrachtungen relevant sind, wobei zu beachten ist,

daß es sich beim 1. Bild um den Write- und beim 2. um den Read-Vorgang handelt – erkennbar an dem R/W-Verlauf! Die entsprechenden Zeitwerte sind in der voran stehenden Tabelle aufgeführt.

| (3) MPU Interface      |                 |      |     |     |      |

|------------------------|-----------------|------|-----|-----|------|

| Chatacteristic         | Symbol          | Min  | Тур | Max | Unit |

| E Cycle                | tc              | 1000 | -   | -   | ns   |

| E High Level Width     | t <sub>WH</sub> | 450  | -   | -   | ns   |

| E Low Level Width      | twi             | 450  | -   | -   | ns   |

| E Rise Time            | t <sub>R</sub>  | -    | -   | 25  | ns   |

| E Fall Time            | t <sub>F</sub>  | -    | -   | 25  | ns   |

| Address Set-Up Time    | tasu            | 140  | -   | -   | ns   |

| Address Hold Time      | tan             | 10   | -   | -   | ns   |

| Data Set-Up Time       | tsu             | 200  | -   | -   | ns   |

| Data Delay Time        | t <sub>D</sub>  | -    | -   | 320 | ns   |

| Data Hold Time (Write) | torrw           | 10   | -   | -   | ns   |

|                        |                 |      |     |     |      |

Bild: Write-Vorgang

Data Hold Time (Read)

Bild: Read-Vorgang

Zunächst wurde ein Übertragungsfehler korrigiert:

Die Timing-Bedingungen sind in *ns* angegeben und nicht in *ms*! Dadurch ergeben sich ganz andere Verhältnisse bei einem Read- bzw. auch beim Write-Vorgang. Die delay150- bzw. delay500-UPs werden nicht mehr gebraucht.

Für die 150ns Vorhaltezeit R/W und /CS reichen die 3 Takte eines rcall = 3x125ns = 375ns völlig aus, hingegen die mind. 500ns für den HIGH-Teil des GLCD-Taktes E mit 4x nop + ein weiterer Befehl gebildet werden. Nun ergibt sich die Schwierigkeit, daß die Daten-Gültigkeit nur 20ns nach der H/L-Flanke von E definiert ist, was wiederum zur Folge hat, daß der nachfolgender Befehl zur Datenauswertung, z.B. sbic portd, 7 nach 125ns wahrscheinlich in's Leere greift!

Wenn man von der L/H-Flanke von E ausgeht, stehen andererseits die Daten aber auch erst nach einer Verzögerung (Delay) von wenigstens 320ns gültig zur Verfügung. Deshalb muß die Datenauswertung vor dem H/L-Befehl eingefügt werden. Beim sbic porto, 7 ist allerdings nicht zu vergessen, daß auch in dem übersprungenen Zweig der GLCD-Takt mit dem H/L-Befehl abzuschließen ist.

Die betreffende Code-Sequenz ändert sich dann wie folgt:

```

BusyCl:

rcall delay150

; wird nicht benötigt, da 3x125ns für rcall BusyCl

: > 150ns

sbi PORTA, 2

; E → HIGH

rcall delay500;

; Impulsanfang, Impulsbreite >500ns

nop

nop

; nach 320ns liegen die gelesenen Daten

nop

; auf dem Datenbus vor

; überspringe nächsten Befehl, wenn PD7 = LOW

sbic PIND, 7

; sonst bei HIGH = interne Op -> warten bis fertig

rjmp BusyCle

nop

cbi PORTA, 2

; E → LOW, Impulsende

ret

; E → LOW, Impulsende

BusyCLe:

cbi PORTA, 2

; für mind. 500ns LOW

nop

nop

nop

nop

rjmp BusyCl

```

Diese spezielle BusyC1-Routine wäre demnach <u>nicht</u> für andere Zwecke zu gebrauchen! Da im Weiteren Read-Vorgänge auch noch für Anderes notwendig sind, ist eine direkte Auswertung am Port ungünstig. Weil die Daten kurz nach der H/L-Flanke nicht mehr zur Verfügung stehen, ist es universell besser, diese in einem Register abzulegen – hier r17.

Die nochmalige Korrektur sieht dann so aus:

```

; wird nicht benötigt, da 3x125ns für rcall BusyCl

BusyCl:

rcall delay150;

: > 150ns

sbi PORTA, 2

; E → HIGH

rcall delay500;

; Impulsanfang, Impulsbreite >500ns

nop

nop

; nach 320ns liegen die gelesenen Daten

nop

; auf dem Datenbus vor

; akt. PIND-Daten, auch noch nach E-LOW

in r17, PIND

; überspringe nächsten Befehl, wenn r17:7 = LOW

sbrc r17, 7

rjmp BusyCle

; sonst bei HIGH = interne Op -> warten bis fertig

cbi PORTA, 2

; E → LOW, Impulsende

ret

; E → LOW, Impulsende

BusyCLe:

cbi PORTA, 2

; für mind. 500ns LOW

nop

nop

nop

: Schleife schließen

rjmp BusyCl

```

## 6.1.1. Test UP GLCD\_init

Jedoch sollte (muss) vorab das UP GLCD\_init unter Einbeziehung der Hardware getestet werden.

Da der ATMega128 die JTAG-Schnittstelle unterstützt, bietet sich hier an, die AVR-Programmierung und die anschließende schrittweise Ausführung des Codes im Hardware-unterstützten JTAG-Simulator durchzuführen.

Realisiert wird das durch den "AVR-JTAG-USB" von <u>www.olimex.com</u>, einem JTAG-ICE-kompatiblen Clone des ATMEL-Gerätes. –

Leider funktioniert das Gerät nicht (mehr) ...

Es wurde die Bestellung eines "USBProg 3.0" von <u>www.embedded-projects.net</u> vorkonfektioniert als "JTAG ICE mkII" und fertig eingespielter Firmware bestellt. Die Lieferung ist noch nicht erfolgt …

#### 6.1.1.1. Test mit dem DRAGON-Board

Eine Alternative sollte das DRAGON-Board von ATMEL bieten. Ein solches liegt vor und nach einigen Ansfangsschwierigkeiten konnte es auch über die JTAG-Schnittstelle mit dem GLCD-Board (ATMegaEvoBoard) angesprochen werden.

Jedoch zeigte sich, daß die im Diassembler-Fenster vonstatten gehende Simulation nicht korrekt ablief. Die Rücklesung (oder auch die Darstellung) des Hex-Codes erfolgte offensichtlich fehlerbehaftet, so daß der Simulator bis zum Ende des Programmspeichers durchlief und dann automatisch abgebrochen wurde. Irgendwelche Step-Funktionen etc. waren nicht ausführbar. Eine Erklärung konnte nicht gefunden werden. In der DRAGON-Hilfe wird vom Setzen der DWEN-Fuse gesprochen. Dies gibt es aber beim ATmega128 nicht, dafür die Fuse OCDEN (ON-Chip-Debugging ON). Das Setzen wird aber immer wieder zurückgenommen, wenn der JTAG-Simulator aktiviert wird.

# 6.1.1.2. Test mit dem Original JTAGICEmkII

Als nächster Versuch wurde ein Original JTAGICEmkII von ATMEL eingesetzt. Auch bei diesem Teil gab es Anfangsschwierigkeiten, d.h. es konnte zunächst keine Kommunikation via USB hergestellt werden. Im Windows-Gerätemanager wurde auch – in Gegensatz zu dem Olimex-Nachbau – kein neues enumeriertes USB-Gerät gefunden. Erst nach einem Upgrade vom ATMEL-Studio heraus konnte wenigstens die Programming-Funktion aktiviert werden. Die USB-Kommunikation läuft offensichtlich immer nur solange, wie die Befehls-/Datenübertragung läuft, ansonsten befindet sich das USB-Grät im "Idle-Mode", d.h. es ist deaktiviert und wird somit in Gerätemanager als virtuelles COM-Port nicht angezeigt.

Damit wurde z.B. die aktuelle Fuse-Programmierung überprüft: JTAGEN und SPIEN waren enabled, d.h. "angehakt", OCDEN nicht. Das wurde nachgeholt, dann das Programmiert-Tool beendet.

Nachfolgend wurde unter "Debug/Select Platform and device..." JTAGICEmkII, ATmega128 und USB ausgewählt. Das Ergebnis ist in der Statusleiste zu sehen. So weit so gut - wenn jetzt aber "Start Debugging" gedrückt wird, so passiert erst mal gar nichts - außer, daß offensichtlich der JTAG-Adapter in laufender Aktion ist (erkennbar am schnellen Flackern der linken grünen LED und "Running" in der Statusleiste). Wird jetzt "BREAK" gedrückt, so wird ein Diassembler-Fenster aufgemacht, der gelbe Zeilenzeiger springt auf die letzte Programmspeicher-Zelle +0000FFFF und "Stopped" wird in der Statuszeile angezeigt. Von dort läßt sich dann nichts mehr bewegen - kein Reset oder sonstige Debug-Funktionen sind wirksam, außer mit "Stopp Debugging" das ganze abzubrechen.

Wird hingegen der "AVR-Simulator" ausgewählt, so funktioniert das Debugging einwandfrei: nach "Start Debugging" und Darstellung eines Fortschrittsbalkens unten über der Statuszeile steht dann der gelbe Zeilenzeiger ordnungsgemäß am Beginn des Programms und man kann mit den zur Verfügung stehenden Debug-Befehlen, wie z.B. "Step" den ASM-Code im einzelnen durchgehen.

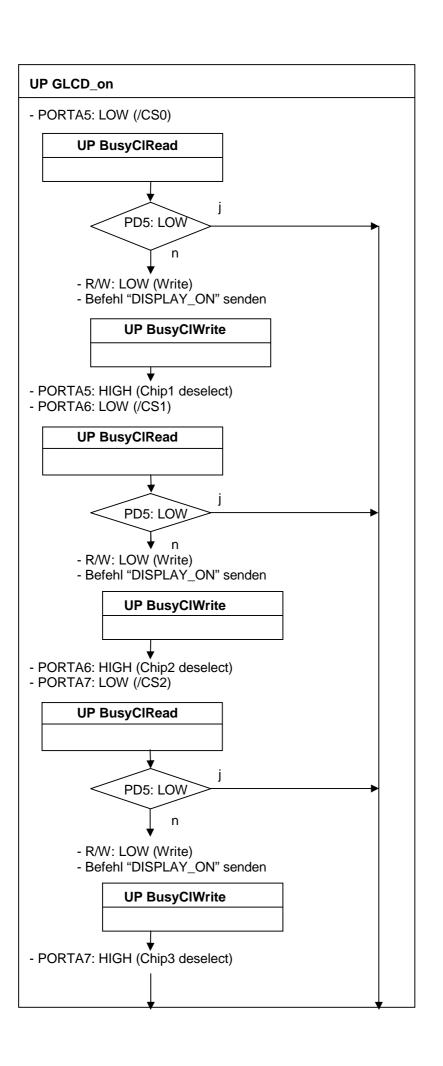

#### 6.2. GLCD ON - Routine

Da nunmehr die 3 Controller des GLCDs bereit sind Befehle zu empfangen, aber auf dem angeschlossenen GLCD noch nichts zu sehen ist (-> testen! – richtig: nur kurzes Aufflackern beim Einschalten, dann "dunkel"), sollte nun der Befehl zum Einschalten des GLCDs gegeben werden.

Dabei ist folgendes zu beachten:

- es müssen immer alle 3 Controller angesprochen werden

- es ist vielleicht zweckmäßig den Einschalt-Befehl erst nach dem Löschen der Daten-RAMs zu geben, damit eine unnötige Darstellung von Zufallsdaten gar nicht erst erfolgt (wird ggf. später noch nachgeholt).

- Da die Routine als UP realisiert werden soll (-> Verwendung nicht nur beim InitProzess), kann <u>nicht</u> davon ausgegangen werden, daß die Controller empfangsbereit

für Befehle, bzw. die vom GLCD gesendeten Daten gültig sind. Wenn die Routine

außerhalb von GLCD\_Init aufgerufen wird, kann auch nicht ausgeschlossen werden,

daß das GLCD bereits eingeschaltet ist.

Deshalb muß hier außer dem GLCDon/off-Bit jedes Mal die "Busy"-Eigenschaft gestestet werden.

```

rcall commlon

; Kommunikation mit 1.Chip an – akt. Daten in r17

GLCD on:

; Status an Bit5 prüfen

sbrs r17, 5

; wenn Bit 5 = 0: Display bereits eingeschaltet

; bei HIGH nächsten Befehl überspringen

rjmp GLCD_on1

; comm1off zum Schließen Chip1

cbi PORTA, 1

; R/W auf LOW setzen – Write

cbi PORTD, 5

; Chip 1 - LCD ein

; Takt – Befehl senden

rcall BusyCl

sbi PORTA, 1

sbi PORTD, 5

; R/W auf HIGH setzen - Read

; zurücksetzen

rcall commloff

; Chip 1 schließen

GLCD_on1:

```

```

rcall comm2on

; Kommunikation mit 2.Chip an – akt. Daten in r17

; Status an Bit5 prüfen

sbrs r17, 5

; wenn Bit 5 = 0: Display bereits eingeschaltet

; bei HIGH nächsten Befehl überspringen

rjmp GLCD_on2

; comm2off zum Schließen Chip2

cbi PORTA, 1

; R/W auf LOW setzen - Write

cbi PORTD, 5

; Chip 2 - LCD ein

: Takt - Befehl senden

rcall BusyCl

sbi PORTA, 1

; R/W auf HIGH setzen - Read

sbi PORTD, 5

; zurücksetzen

rcall comm2off

; Chip 2 schließen

GLCD on2:

rcall comm3on

; Kommunikation mit 3.Chip an – akt. Daten in r17

; Status an Bit5 prüfen

sbrs r17, 5

; wenn Bit 5 = 0: Display bereits eingeschaltet

; bei HIGH nächsten Befehl überspringen

; comm3off zum Schließen Chip3

rjmp GLCD_on3

: R/W auf LOW setzen - Write

cbi PORTA, 1

cbi PORTD, 5

; Chip 3 - LCD ein

; Takt – Befehl senden

rcall BusyCl

sbi PORTA, 1

; R/W auf HIGH setzen - Read

sbi PORTD, 5

; zurücksetzen

rcall comm3off

; Chip 3 schließen

GLCD on3:

ret

```

Damit müsste das GLCD eingeschaltet sein, d.h. die in den internen RAM's der 3 Chips abgespeicherten Daten müssten nun als Pixel eingeschaltet zu sehen sein.

#### 6.2.1. Test UP GLCD on

Nach dem Einspielen der Firmware einschließlich der Funktionen GLCD\_init und GLCD\_ON ist nach *Reset* oder dem Zuschalten der Stromversorgung nichts zu sehen. Auch das anfängliche Flackern auf den Bildschirm ist nun nicht mehr vorhanden. Inwieweit die beiden o.g. Funktion korrekt laufen, kann so ohne weiteres nicht ermittelt werden.

Ein "Trockentest" mit dem AVR-Simulator im ATMEL-Studio könnte zwar in gewissem Maße Aufschluss geben, ist jedoch sehr zeitaufwändig und außerdem lassen sich damit nicht die konkreten Anschalt-Bedingungen des GLCD's prüfen. Eine "In-Circuit-Emulation" über die JTAG-Schnittstelle und eines dementsprechenden Prüfadapters sollten dann schon aufschlussreichere Ergebnisse bringen.

Die JTAG-Simulation muß derzeit ausgesetzt werden, solange kein funktionierender Prüfadapter zur Hand ist, bzw. die Debugging-Funktion im AVR-Studio nicht richtig funktioniert – siehe 6.1.1. Test UP GLCD\_init.

Nach den Erkenntnissen unter <u>6.3.1.</u> muß die Routine GLCD\_on noch mal überarbeitet werden (Befehl fehlt noch???) ... -> ist erledigt!

#### **6.2.1.1.** Alternative Test-Instrumentarien

Da z.Zt. kein funktionierendes Equipment für einen In-Circuit-Test zur Verfügung steht, muß mit Hilfslösungen gearbeitet werden. Dazu werden in gewohnter Weise an relevanten Stellen im Code sog. Test-Sequenzen eingebaut, wo dann über einen Prüfport und LED-Anzeige bestimmte Zustände signalisiert werden können.

Das Prüf-Port PORTC muß zunächst initialisiert werden:

```

clr r16 ; alle C-Pins auf LOW out PORTC, r16 ldi r16, 0bll111111 ; alle auf Ausgabe out DDRC, r16

```

So kann z.B. das zum UP BusyCl Erwähnte eingeführt werden in BusyCl\_new:

```

BusyCl:

. . .

; E → LOW, Impulsende

BusyCLe:

cbi PORTA, 2

; für mind. 500ns LOW -

; wird durch nachfolgende Befehlssequenz erfüllt

; Hochzählen bis 255 -> 0

inc r18

breq BusyClo

nop

nop

; Schleife schließen

rjmp BusyCl

BusyClo:

sbi PORTC, 7

; PC7 auf HIGH - LED_7 an

; Endlosschleife – raus nur über Reset!

rjmp BusyClo

```

Andererseits besteht auch die Möglichkeit die Abarbeitung einzelner UPs zu signalisieren. Dazu wird z.B. in GLCD\_main folgendes eingeführt:

```

GLCD_main: sbi PORTC, 0 ; nur zum Test: Init ok - LED_0 ;

rcall GLCD_init ; UP zur AVR-Port- und LCD-Initialisierung sbi PORTC, 1 ; nur zum Test; GLCD_init ok - LED_1 ;

rcall GLCD_on ; Graphic-LCD einschalten ; nur zum Test: GLCD_on ok - LED_2 ;

```

Das ist z.Zt. implementiert und die korrekte Funktion konnte soweit nachgewiesen werden. Die LEDs 0 bis 2 gehen an (ok), aber auch die Kontroll-LED\_7, wobei es noch nicht geklärt ist, warum sich diese angeschaltet wird, d.h. sich der LCD-Controller "aufgehängt" hat.

#### 6.2.1.2. Test mit JTAGICEmkII

Das Problem mit dem JTAG-Adapter scheint nun gelöst zu sein, jedenfalls konnte bei Verwendung des Original JTAGICEmkII von ATMEL die Ursache der inkorrekten Funktionsweise der Debugger-Funktion gefunden werden:

Die Stromversorgung auf dem "ATMegaEvo-Board" war durch einen zu klein bemessenen Ladekondensator nach dem Graetz-Gleichrichter zu unstabil, d.h. der nachfolgende Linearregler LM317 konnte das nicht mehr ausregeln und somit ging das Board alle 25ms in den RESET-Zustand. Dazu gibt es eine Diskussion im Forum von www.mikrocontroller.net/forum/mikrocontroller-elektronik/avr - Suche AVR JTAGICEmkII Debug-Probleme.

Der anschließende Testlauf – STEP, wie auch RUN über den JTAGICE verliefen nun scheinbar erfolgreich. Eine detaillierte Untersuchung wurde zunächst nicht durchgeführt, da offensichtliche Fehler nicht erkennbar waren.

Das Problem, daß sich der LCD-Controller "aufgehängt" hat, konnte durch eine Programmänderung am Schluß beseitigt werden:

GLCD\_end: rjmp GLCD\_end ; Endlosschleife

Offensichtlich ist die vorhergehende Loop-Schleife zu GLCD\_main unverträglich mit der Initialisierung – ohne das jetzt näher untersuchen zu wollen.

Es sieht so aus, als ob auf dem GLCD alle Pixel eingeschaltet sind.

Da von der nachfolgenden Löschung aller Pixel mit GLCD\_clr auf dem Display nichts zu sehen war, muß evtl. doch davon ausgegangen werden, daß das Display nicht eingeschaltet worden ist. Eine genauere STEP-by-STEP-Untersuchung soll dazu Klarheit bringen.

In der Tat kam keine Einschaltung zu Stande, weil im UP GLCD\_on der Befehl "Display-Einschalten" falsch, bzw. überhaupt nicht vorhanden war.

#### Aus diesem Grunde wurde GLCD\_on verändert:

```

; Kommunikation mit 1.Chip an - akt. Daten in r17

GLCD on:

rcall comm1on

: Status an Bit5 prüfen

; wenn Bit 5 = 0: Display bereits eingeschaltet

sbrs r17, 5

; bei HIGH nächsten Befehl überspringen

rjmp GLCD on1

; Comm1off zum Schließen Chip1

; R/W auf LOW setzen - Write

cbi PORTA, 1

; Chip 1 - LCD ein :-> FALSCH!

cbi PORTD, 5

; Befehl DISPLAY_on

ldi r16, 0b00111111

out PORTD, r16

rcall BusyCl

; Takt

; R/W auf HIGH setzen - Read

sbi PORTA, 1

;sbi PORTD, 5

; zurücksetzen – unnütz!

rcall commloff

; Chip 1 schließen

GLCD on1:

; Kommunikation mit 2.Chip an - akt. Daten in r17

rcall comm2on

: Status an Bit5 prüfen

; wenn Bit 5 = 0: Display bereits eingeschaltet

sbrs r17, 5

; bei HIGH nächsten Befehl überspringen

; Comm2off zum Schließen Chip2

rjmp GLCD_on2

cbi PORTA, 1

; R/W auf LOW setzen - Write

; Chip 2 - LCD ein :-> FALSCH!

cbi PORTD, 5

ldi r16, 0b00111111

; Befehl DISPLAY_on

out PORTD, r16

rcall BusyCl

; Takt

sbi PORTA, 1

; R/W auf HIGH setzen - Read

;sbi PORTD, 5

; zurücksetzen – unnütz!

; Chip 2 schließen

rcall comm2off

GLCD_on2:

rcall comm3on

; Kommunikation mit 3.Chip an - akt. Daten in r17

; Status an Bit5 prüfen

sbrs r17, 5

; wenn Bit 5 = 0: Display bereits eingeschaltet

; bei HIGH nächsten Befehl überspringen

; comm3off zum Schließen Chip3

rjmp GLCD_on3

cbi PORTA, 1

; R/W auf LOW setzen - Write

; Chip 3 - LCD ein :-> FALSCH!

cbi PORTD, 5

ldi r16, 0b00111111

; Befehl DISPLAY_on

out PORTD, r16

rcall BusyCl

; Takt

sbi PORTA, 1

; R/W auf HIGH setzen - Read

; zurücksetzen – unnütz!

;sbi PORTD, 5

rcall comm3off

; Chip 3 schließen

GLCD on3:

ret

```

Diesmal wurde das Einschalten des Displays = Anzeige aller Pixel beobachtet. Es erwies sich als notwendig, den Kontrast entsprechend einzuregulieren, so daß beim Display\_off auch keine Pixel mehr zu sehen sind.

## 6.3. UP GLCD clr

Die Bearbeitung dieser Funktion wird derzeit ausgesetzt, solange keine Notwendigkeit zur Anwendung besteht.

Da nun feststeht, daß alle Pixel nach der GLCD-Initialisierung zunächst eingeschaltet sind (so sieht es jedenfalls aus), besteht nun ggf. doch die Notwendigkeit diese zu löschen.

Funktional muß dazu in die 3 GLCD\_RAM-Bereiche (0,0; 63,63), (64,0; 127,63), (128,0; 191,63) jeweils "0" eingetragen werden.

Dazu muß zunächst die Startadresse bereitgestellt werden in dem UP:

```

GLCD adrSt: ldi r16, 0b01000000 ; Befehl "SetAdrY 0"

out PORTD, r16

ldi R16, 0b11100000 ;/CS0 -/CS2 deaktiviert -

; R/W = LOW, RS = LOW (Befehl)

out PORTA, R16

ldi r16, 0b11111111 ; PORTD auf Ausgang out DDRD, r16 ; damit liegt der Befehl am GLCD an

rcall Commlon

; Kommunikation mit dem 1. Chip an

rcall Commloff ; Kommunikation mit dem 1. Chip aus

rcall Comm2on

; Kommunikation mit dem 2. Chip an

rcall Comm2off

; Kommunikation mit dem 2. Chip aus

rcall Comm3on

; Kommunikation mit dem 3. Chip an

rcall Comm3off

; Kommunikation mit dem 3. Chip aus

```

Da die Sequenz reall Commlon/reall commloff usw. schon im UP GLCD\_init vorkommt kann diese – nach Einführung des Labels GLCD\_comm: - vereinfacht werden: reall GLCD comm

Weiter geht es dann mit:

```

ldi r16, 0b10111000 ; Befehl "SetAdrX_0"

out PORTD, r16

;

rcall GLCD_comm

;

ret

;

```

Damit sind die 3 Controller-Chips auf dem GLCD für die Datenaufnahme vorbereitet.

Im UP GLCD\_clr geht es dann weiter mit:

```

ldi r16, 0b11100001 ;/CSO -/CS2 deaktiviert -

out PORTA, r16 ; R/W = LOW, RS = HIGH (Daten)

clr r16 ; alle Pixel aus

; com r16 ; oder alle Pixel an

; werden beide Befehle auskommentiert,

; wird das aktuelle Pixelmuster in r16 übertragen

out PORTD, r16

```

Daß mit jeder Datenübertragung der interne AdresszählerX der Chips automatisch inkrementiert, ist zwar für den Übertragungsprozeß einfacher, aber trotzdem muß die Anzahl der übertragenen Bytes kontrolliert werden. Das geht am besten mit einem virtuellen externen Adresszähler x19, welcher jedoch im Gegensatz zu dem internen Chip-Adresszähler abwärts zählt. Damit ist ein günstigeres Abbruch-Kriterium gegeben.

```

ldi r19, 64

; virtuellen Chip-Adresszähler laden

; interner Adresszähler + 1

rcall GLCD_comm1

GLCD_clr1:

rcall GLCD_comm1off

dec r19

; solange bis r19 = 0

brne GLCD clr1

ldi r19, 64

; virtuellen Chip-Adresszähler laden

rcall GLCD_comm2

; interner Adresszähler + 1

GLCD_clr2:

rcall GLCD_comm2off

dec r19

; solange bis r19 = 0

brne GLCD_clr2

ldi r19, 64

; virtuellen Chip-Adresszähler laden

; interner Adresszähler + 1

GLCD_clr3:

rcall GLCD_comm3

rcall GLCD comm3off

dec r19

brne GLCD_clr3

; solange bis r19 = 0

```

Damit sollten die ersten 8 Zeilen = 1.Page des GLCD gelöscht sein.

Für die weiteren 6 Pages = 56 Zeilen muß das gleiche Prozedere ebenfalls durchgeführt werden, wobei es kein Auto-Increment beim Page-Zähler gibt. Es muß also nach jeder Page-Sequenz die neue Page-Adresse separat übertragen werden.

Grundsätzlich wäre zu untersuchen, ob es günstiger ist, die Übertragung Page-weise für alle 3 Chips nacheinander – wie oben begonnen – oder Chip-weise die Pages vollständig abzuarbeiten.

In jedem Fall sollte aus Vereinfachungs-Gründen wiederholte Funktionalität als weitere UP ausgegliedert werden.

## 6.3.1. Testergebnis GLCD\_clr

Nach dem Laden des Programms konnte keine Veränderung der GLCD-Ausgabe festgestellt werden. Offensichtlich gibt es auch Kommunikationsprobleme, denn die Busy-LED(7) leuchtet (-> "aufgehangen" in Endlosschleife)

Der Test über JTAG kommt zu folgendem Ergebnis:

Im UP Busycl kommt es zu Konflikten, da je nach Situation das Datenrichtungsregister DDRD von PORTD nicht immer auf Eingang geschaltet ist und außerdem nicht sichergestellt ist, daß R/W auf HIGH liegt, somit kein Status eingelesen werden kann. Des Weiteren wird mit dem Einlesen des Status der eigentliche Befehl nicht an den GLCD-Controller übermittelt. Das UP Busycl muß also in zwei Sequenzen aufgeteilt werden:

- BusyCL zur Ermittlung der Befehls-Bereitschaft des Chips

- Instrcl zur Übermittlung des Befehls

Das UP Busycl wurde dementsprechend ergänzt:

```

in r15, PORTA

: PORTA-Status sichern

BusyCl:

; Datenrichtung PORTD sichern

in r14, DDRD

clr r16

; PORTD auf Eingang umschalten,

; - Inhalt bleibt erhalten

out DDRD, r16

cbi PORTA, 0 ; RS = 0: Befehl sbi PORTA, 1 ; R/W = HIGH (Read-Status)

; rcall delay150; wird nicht benötigt, da 3x125ns für rcall BusyCl

: > 150ns

sbi PORTA, 2

; E -> Taktimpuls HIGH

rcall delay500;

; Impulsanfang, Impulsbreite >500ns

nop

nop

; nach 320ns liegen die gelesenen Daten

nop

; auf dem Datenbus vor

; akt. PIND-Daten sichern, auch noch nach E-LOW

in r17, PIND

sbrc r17, 7

; überspringe nächsten Befehl, wenn r17:7 (Busy) = LOW

sbrc r17, 7

rjmp BusyCle

cbi PORTA, 2

; sonst bei HIGH = interne Op -> warten bis fertig

; E -> LOW, Impulsende

out PORTA, r15 : PORTA-Status wieder herstellen

InstrCL:

out DDRD, r14

; Datenrichtung PORTD wieder herstellen

; E -> Taktimpuls HIGH

sbi PORTA, 2

nop

nop

nop

```

```

cbi PORTA, 2 ; E -> LOW, Impulsende ; ret ;

BusyCLe: cbi PORTA, 2 ; E -> LOW, Impulsende ; für mind. 500ns LOW - ; wird durch nachfolgende Befehlssequenz erfüllt inc r18 ; Hochzählen bis 255 -> 0 breq BusyClo ; nop nop rjmp BusyCl ; Schleife schließen ;

BusyClo: sbi PORTC, 7 ; PC7 auf HIGH - LED an ; Endlosschleife - raus nur über Reset! :

```

Ggf. kann (muß) die Routine InstrCl als separates UP ausgegliedert werden. Dann ist jedoch die Datensicherung in r15, r14 entsprechend vorzubereiten.

Der weitere Test über JTAG ergab, daß nur das erste Pixel-Byte ganz links gelöscht wurde. Alles andere blieb so, wie es ist. Somit wird also auch die Information nur an den 1. GLCD-Controller übertragen und die anderen beiden "gehen leer aus" ???

Bei einem STEP/RUN-Test mit Haltepunkt bei brne GLCD\_pg1 im UP GLCD\_page konnte die Wirksamkeit der Routine nachgewiesen werden. Wird hingegen die Schleife GLCD\_pg1 ohne Unterbrechung abgearbeitet, so ist kein Löschen zu sehen. Das Einbringen eines 150µs-Delay gleich nach Comm\_off (auch bei GLCD\_pg2 und GLCD\_pg3 war dann erfolgreich. Warum???

Bemerkenswert ist, daß ein Reset oder ein kurzes Unterbrechen der Stromversorgung die RAM-Zellen der GLCD-Controller nicht dazu veranlasst, ihre Informationen zu "vergessen", d.h. wieder auf HIGH zu gehen. Erst eine längere Pause von mehr als 1 Minute ist dazu notwendig!

## Ergänzung der Routine GLCD\_pages

Wie schon weiter oben beschrieben, ist die Page-Adressierung nicht automatisch inkrementierend, so wie bei der X-Adressierung.

Deshalb wurde nachfolgende Erweiterung von GLCD\_pages vorgenommen:

```

GLCD_pages: ldi r20, 8 ; virtuellen Chip-Pagezähler laden GLCD_pgs1: rcall GLCD_page ;

```

```

; sicherheitshalber Z-Flag löschen

clz

dec r20

brne GLCD_pgs2

; solange bis r20 = 0

ret

; Pixeldaten sichern (wichtig!)

GLCD_pgs2:

in r16, PORTD

push r16

mov r16, r20

: sichere r20

com r16

; invertiere Wert

; +1

inc r16

cbr r16, 0b01000000 ; lösche Bit6, damit "SetAdrX"-Befehl ok

out PORTD, r16

cbi PORTA, 0

; RS = LOW (Befehl)

rcall Comm1on

; Kommunikation mit dem 1. Chip an

; Kommunikation mit dem 1. Chip aus

rcall Commloff

; Kommunikation mit dem 2. Chip an

rcall Comm2on

; Kommunikation mit dem 2. Chip aus

rcall Comm2off

; Kommunikation mit dem 3. Chip an

rcall Comm3on

rcall Comm3off

; Kommunikation mit dem 3. Chip aus

; Pixeldaten zurück

pop r16

out PORTD, r16

; RS = HIGH (Daten)

sbi PORTA, 0

; nächste Page übertragen

rjmp GLCD pgs1

```

Nunmehr sind die Routinen des UP GLCD\_clr vollständig, d.h. die Pixel-Löschung nach dem Einschalten war erfolgreich auf der ganzen GLCD-Fläche. Jedoch ist die Effizienz noch nicht so ganz befriedigend, weil trotz einer Ausführungszeit von ??? ms der ganze Vorgang zu beobachten ist. Hier gibt es sicherlich noch Optimierungsbedarf. Ungeklärt ist vor allem noch, woraus sich die Notwendigkeit der Einschiebung einer 150ms-Verzögerung (delay150) in die GLCD\_pg-Schleife nach jedem RAM-Zugriff ergibt (siehe weiter oben die Bemerkung zum STEP/RUN-Test). Im Datenblatt des GLCD-Controllers KS108b steht eine minimale Vorhaltezeit von 140ns für R/W, /CS und RS, bevor die steigende Taktflanke E anliegt. Für Daten sind es sogar mindestens 200ns.

Bei 16MHz Taktfrequenz des ATmega128 ergibt sich pro Takt 62,5ns, so daß es eigentlich mit 3 Takten getan sein müsste, auch wenn die Haltezeit von ca. 20ns noch berücksichtigt wird. Anders sieht es mit der minimalen LOW/HIGH-Zeit des GLCD-Controllers E aus, welche mit jeweils mindestens 450ns, bzw. mit 1000ns für die gesamt

E-Zeit vorgegeben ist. Damit ergibt sich, daß zwischen 2 Takten E mindestens 16 Takte des ATMega128 liegen müssen. Das ist in der GLCD\_pgx-Schleife <u>nicht</u> der Fall und dort liegt ja auch das Problem.

Warum dieses offensichtlich nur beim Datentransfer in den RAM vorhanden ist – und nicht auch beim RS-, R/W-Timing – ist noch nicht geklärt!

Die Einfügung von 3x nop anstelle des delay150 löst das Problem noch nicht.

Aus Optimierungsgründen ist es erforderlich, die minimale nop-Anzahl zu bestimmen.

Des Weiteren ist es aus Performence-Gründen vielleicht möglich, den AutoIncrement-Zugriff auf das RAM zu machen, ohne jedes Mal den Controller zu deaktivieren. Dann kann allerdings nicht mit den jetzt verfügbaren allgemeinen UPs GLCD\_commx gearbeitet werden.

## 6.3.2. Schlussfolgerungen zur Weiterentwicklung

Die bisherigen Untersuchungen zeigte die prinzipielle Möglichkeit der Kommunikation des ATMega128 mit dem GLCD-ControllerSet. Einige Fragen, bzw. Unklarheiten bestehen zwar immer noch, aber aus den gewonnenen Erfahrungen sollten für die Weiterentwicklung einige Richtungs-weisende Schlussfolgerungen gezogen werden:

- Erstellung eines Flussdiagramms zur besseren Übersicht und Verständlichkeit,

- weitere Modularisierung des Gesamtpaketes der GLCD-Routinen,

- Optimierung der einzelnen UPs

- ggf. neues Projekt im ATMEL-Studio

(hier weiter)

# 6.3.2.1. Flussdiagramm

## **UP GLCD\_clr**

# **UP GLCD\_adrSt** - PORTD: 0b01000000 (SetAdrY\_0) - PORTA: 0b11100000 (/CS0 - /CS2 HIGH -R/W = LOW, RS = LOW (Befehl) - PORTD: Output Comm1\_on Comm1\_off Comm2\_on Comm2\_off Comm3\_on Comm3\_off - PORTD: 0b10111000 (SetAdrX\_0) Comm1\_on Comm1\_off Comm2\_on Comm2\_off Comm3\_on Comm3\_off

- PORTA: 0b11100001 (/CS0 /CS2 deaktiviert R/W = LOW, RS = HIGH (Daten)

- PORTD: 0b00000000 (alle Pixel aus)

UP GLCD\_pages

| UP GLCD_pages                             |              |  |  |  |

|-------------------------------------------|--------------|--|--|--|

| R20: 8 (virtuellen Pagezähler/Chip laden) |              |  |  |  |

|                                           | UP GLCD_page |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

|                                           |              |  |  |  |

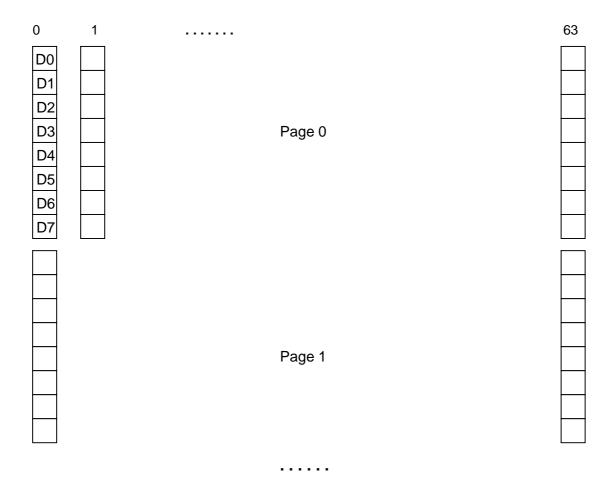

#### 6.4. Struktur des Display-RAMs

Zunächst soll in einem Versuch geklärt werden, wie sich ein Daten-Byte auf dem GLCD abbildet. Dazu wird in einer Test-Sequenz auf die X-Adresse 0, Page-Adresse 0 z.B. das Byte 0b10101010 ausgegeben (geschrieben).

Die o.g. Sequenz wurde so nicht implementiert, weil schon durch das UP GLCD\_clr die RAM-Struktur hinreichend geklärt wurde. Es ist tatsächlich so, daß auf der X-Achse (GLCD – Y-Adresse!) von links nach rechts gezählt wird – und zwar 64 Byte senkrecht nebeneinander. Es werden also 8 Pixel in 8 Zeilen untereinander mit der gleichen Y-Adresse angesprochen (siehe dazu in der <u>Befehlsliste</u> des GLCD-Controllers (2) "SetAdress (Y)"). Das betrifft den 1.Controller. Der 2.Controller zählt zwar wieder von 0 – 63, betrifft aber jetzt die Pixel 65 – 128 auf dem GLCD. Der 3. Controller verwaltet die Pixel 129 – 192.

Zu überprüfen wäre jetzt noch, ob tatsächlich die Reihenfolge im DatenByte D0 ... D7 mit der Reihenfolge der Zeilen 1 ... 8 von oben nach unten übereinstimmt. Dazu wird der Einfachheit halber versuchsweise im UP GLCD-clr für das zu schreibende Byte ein \$E1 eingesetzt, welches sich aus dem aktuellen Status von PORTA ergibt. Damit müssten die Zeilen 1-3 und 8 eingeschaltet und 4-7 ausgeschaltet sein. Praktisch braucht nur im UP GLCD\_clr der Befehl clr r16 deaktiviert werden.

Wegen der Probleme mit dem lang andauerndem Speichererhalt (siehe unter <u>Testergebnisse</u> den "bemerkenswerten" Hinweis) war auch schon ein Schreiben mit \$FF erfolgreich.

## **Ergebnis**

Die Zeilen-Reihenfolge in Abhängigkeit der Bit-Stellung im Datenbyte ist genau so wie erwartet, d.h. Bit0 liegt auf Zeile 1 usw. und Bit7 auf Zeile 8. Die Darstellung in (2) der Befehlsliste ist richtig!

## Zu prüfende Funktionalität:

Nach dem ein (mehrere) Byte in das/die GLCD-RAM geschrieben wurde, sollen diese mit dem Daten-Lesebefehl wieder zurück gelesen werden.

Siehe dazu <u>6.7.</u>

#### 6.5. UP GLCD SetX

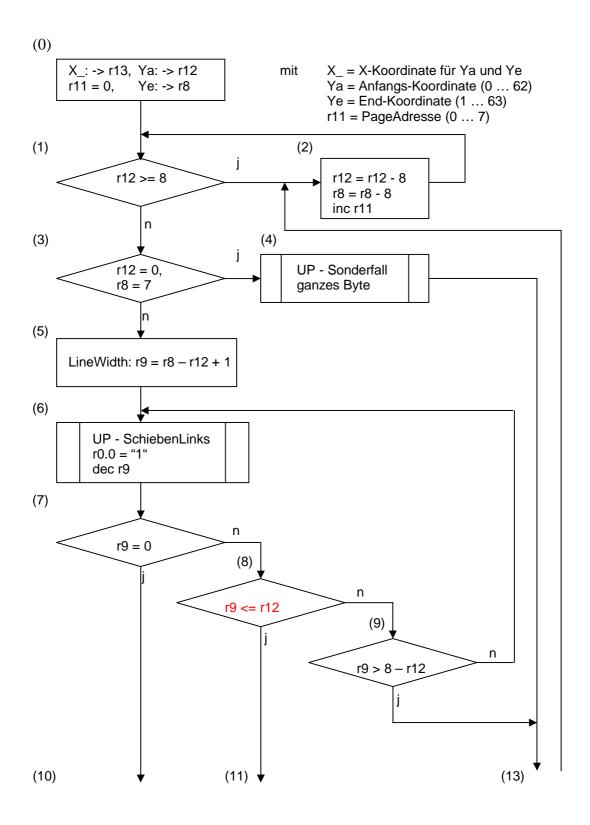

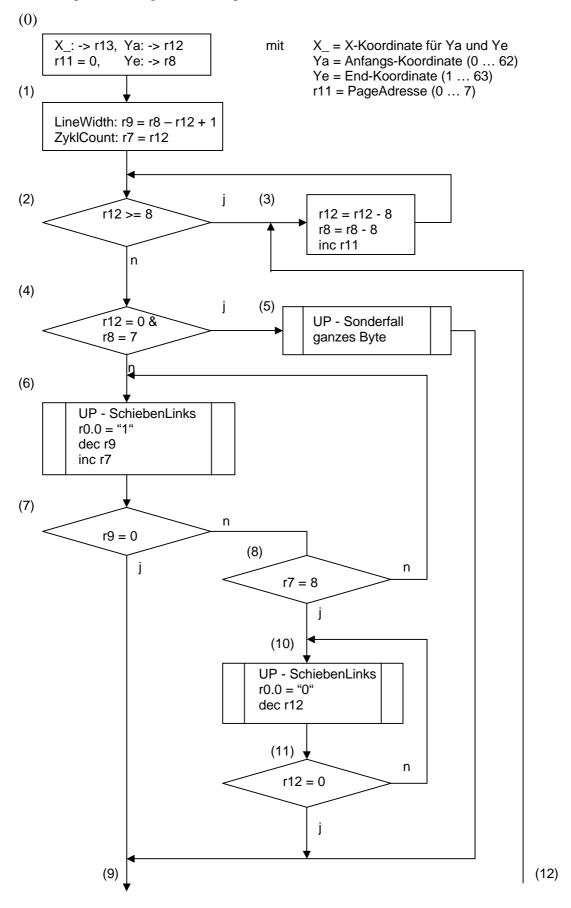

Mit diesem Unterprogramm soll die aktuelle X-Adresse gesetzt werden. Diese geht bei dem hier verwendeten GLCD von  $0 \dots 191$  (3x 64 = 192 Pixel auf einer Zeile). Es ist also je nach X-Wert noch zwischen den 3 LCD-Controllern zu unterscheiden.

Das UP GLCD\_setx ist im Zusammenhang mit dem UP GLCD\_setY die

Grundvoraussetzung zum Setzen, bzw. Löschen eines Pixels.

Zu beachten ist, daß der dazu betreffende Befehl "SetAdrY" zu verwenden ist!

Dieser wurde bereits schon im UP GLCD\_adrst eingesetzt.

Die Parameter-Übergabe "AdrX" (0 ... 191) erfolgt in r13.

```

ldi r16, 0b10111111 ; 191

GLCD_SetX:

sub r16, r13

; prüfen, ob AdressWertX > 191

brcc SetXo

; Fehler!

sbrs r13, 6

; überspringe nächsten Befehl, wenn Bit6 gesetzt (>63)

rjmp SetX1

; AdrWertX <=63

; überspringe nächsten Befehl, wenn Bit7 gesetzt (>127)

sbrs r13, 7

rjmp SetX2

; 63 < AdrWert > 127

; virt. Adressähler unverändert lassen

mov r16, r13

andi r16, 0b00011111 ; Ausmaskieren der Bits > 31

sbr r16, 0b01000000 ; damit Befehl "SetAdrY" komplett

or r16, r13

; damit Befehl + Adresse für den betreffenden LCD-Chip

; wird nicht mehr gebraucht

out PORTD, r16 ; an PORTD senden ldi R16, 0b11100000 ; /CS0 - /CS2 deaktiviert - out PORTA, r16 ; R/W = LOW, RS = LOW

; R/W = LOW, RS = LOW (Befehl)

1di r16, 0b11111111 ; PORTD auf Ausgang

out DDRD, r16

; damit liegt der Befehl am GLCD an

; Übertragen auf Chip3

rcall Comm3_on

rcall Comm3 off

rjmp SetXend

SetX1:

mov r16, r13

andi r16, 0b00011111 ; Ausmaskieren der Bits > 31

sbr r16, 0b01000000 ; damit Befehl "SetAdrY"

out PORTD, r16

; damit Befehl+Adresse für den betreffenden LCD-Chip

; an PORTD senden

out PORTD, r16 ; an PORTD senden ldi R16, 0b11100000 ;/CSO -/CS2 deaktiviert -

; R/W = LOW, RS = LOW (Befehl)

out PORTA, r16

ldi r16, 0b11111111 ; PORTD auf Ausgang

; damit liegt der Befehl am GLCD an

out DDRD, r16

; Übertragen auf Chip1

rcall Comm1 on

rcall Comm1_off

rjmp SetXend

```

```

SetX2:

mov r16, r13

andi r16, 0b000011111 ; Ausmaskieren der Bits > 31

sbr r16, 0b01000000 ; damit Befehl "SetAdrY"

; or r16, r13 ; damit Befehl + Adresse für den betreffenden LCD-Chip

out PORTD, r16 ; an PORTD senden

ldi R16, 0b11100000 ; /CS0 - /CS2 deaktiviert -

out PORTA, r16 ; R/W = LOW, RS = LOW (Befehl)

ldi r16, 0b11111111 ; PORTD auf Ausgang

out DDRD, r16

; damit liegt der Befehl am GLCD an

rcall Comm2_on

; Übertragen auf Chip2

rcall Comm2_off

SetXend:

ret

sbi PORTC, 7

; PC7 auf HIGH - LED "Störung" ein

SetXo:

; Endlosschleife - raus nur über Reset!

rjmp SetXo

;

```

Zunächst erfolgt eine Prüfung auf Zulässigkeit des Adress-Wertes.

Die Selektierung der Adress-Werte auf die 3 LCD-Controller erfolgt über die Auswahl Bit6, Bit7 des Adress-Wertes und nach Ausmaskieren der unteren 5 Bits durch Zuweisung über die UP Commx\_on / Commx\_off.

#### 6.5.1 Test

Der Test mit dem JTAGICEmkII verlief zunächst negativ, weil die rot gekennzeichneten Programm-Schritte nicht korrekt waren.

#### Korrektur:

Nach Korrektur schien die X-Adressierung einwandfrei zu funktionieren.

#### 6.6. UP GLCD\_SetY

Mit diesem Unterprogramm soll die aktuelle "X-Adresse" (Page-Adresse) gesetzt werden. Diese geht bei dem hier verwendeten GLCD von 0 ... 7. Eine Page-Adresse beinhaltet immer 8 Bits vertikal untereinander, d.h. die Zeilen 1 ... 8 haben die Page-Adresse "0", die Zeilen 9 ... 16 die Page-Adresse "1" usw. Um ein bestimmtes Pixel innerhalb einer Page-Adresse ansprechen zu können, muß noch eine Auswahl getroffen werden, was z.B. in Form einer Maske geschehen kann, die über das Daten-Byte gelegt wird. Die dazu notwendigen 8 Masken werden dann zweckmäßigerweise als Konstanten in einer Tabelle mit im Programmcode abgelegt. Zur Adressierung der Masken wird dann mit einem Adress-Offset gearbeitet, der invers zum Pixel-Standort im Datenbyte ist, z.B. Pix1 = D7.

```

ldi r16, 0b10000111 ;191

GLCD_SetY:

sub r16, r12

; prüfen, ob PageAdressWertY > 7

; Fehler!

brcc SetXo

ldi r16, 0b10111000 ; Befehl "SetAdrX_0"

or r16, r12 ; damit Befehl + Adresse out PORTD, r16 ; an PORTD an

ldi r16, 0b11111111 ; PORTD auf Ausgang

; damit liegt der Befehl am GLCD an

out DDRD, r16

; alle 3 Chips

rcall Comm1_on

rcall Comm1_off

rcall Comm2_on

rcall Comm2_off

rcall Comm3_on

rcall Comm3_off

ret

; PC7 auf HIGH - LED "Störung" ein

sbi PORTC, 7

SetXo:

; Endlosschleife - raus nur über Reset!

rjmp SetXo

```

Zunächst erfolgt eine Prüfung auf Zulässigkeit des Adress-Wertes.

Eine Selektierung auf einen der drei GLCD-Chips braucht hier nicht zu erfolgen, da die Y-Adresse für alle gleich ist.

Damit es zu keiner Verwechslung kommt, wurde die Bezeichnung des UP GLCD\_SetY in GLCD\_SetP geändert (siehe <u>6.6.1 Test</u> und Korrektur). Somit wird in diesem Zusammenhang auch nicht mehr von der Y-Adresse, sondern nur noch von der **Page**-Adresse gesprochen. Weitere Auswirkungen hat das zunächst nicht – außer, daß die

eigentliche Y-Adresse für den Zugriff auf ein einzelnes Pixel innerhalb der Page-Adresse noch bestimmt werden muß.

#### 6.6.1 Test

Auch dieser Test mit den JTAGICEmkII verlief zunächst nicht positiv, weil noch einige Programmfehler (rot markiert) vorhanden waren.

## Korrektur:

Nach Korrektur schien die Page-Adressierung einwandfrei zu funktionieren.

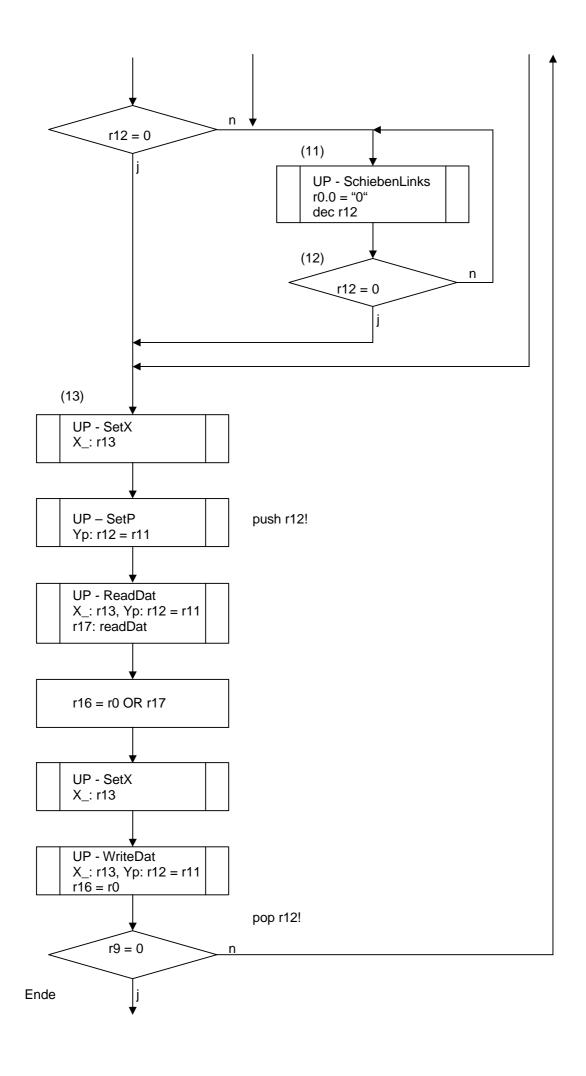

#### 6.7. UP GLCD\_read

Das UP GLCD\_read ist wichtig für die Manipulation des GLCD-RAMs. Da dieser rücklesbar ist, macht es keinen Sinn im μC noch einmal extra einen Display-RAM aufzubauen. Der Aufbau des GLCD-RAMs ist unter "6.4. Struktur des Display-RAMs" erläutert. Danach liegen die Pixel eines Daten-Bytes senkrecht untereinander. Zur Manipulation eines beliebigen Pixels ist zunächst dessen X-Adresse zu bestimmen, danach die Page-Adresse, worin sich das Pixel befindet. Mit diesen Adress-Werten wird das betreffende Daten-Byte ausgelesen.

```

; Gültigkeit r13 ungeprüft, da im UP GLCD_SetX

GLCD_read:

sbrs r13, 6 ; überspringe nächsten Befehl, wenn Bit6 gesetzt (>63) rjmp rd1 ; AdrWertX <=63

sbrsr13, 7; überspringe nächsten Befehl, wenn Bit7 gesetzt (>127)rjmprd2; 63 < AdrWert > 127

ldi R16, 0b11100011 ;/CS0 -/CS2 deaktiviert -

out PORTA, r16; R/W = HIGH (Lesen), RS = HIGH (Daten)

cls r16 ; PORTD auf Eingang

out DDRD, r16 ; damit ist PORTD für den Datenempfang bereit

;rcall Comm3_on ; Übertragen auf Chip3 - wird hier nicht verwendet

cbi PORTA, 7 ; setze PORTA7 (/CS2) auf LOW

rcall BusyClread1; Takt

;rcall Comm3_off

sbi PORTA, 7; setze PORTA7 (/CS2) wieder auf HIGH

rjmp rdEnd

cbi PORTA, 5; setze PORTA5 (/CS0) auf LOW

rd1:

rcall BusyClread1; Takt

sbi PORTA, 5 ; setze PORTA5 (/CS0) wieder auf HIGH

rjmp rdEnd

cbi PORTA, 6; setze PORTA6 (/CS1) auf LOW

rd2:

rcall BusyClread1 ; Takt

sbi PORTA, 6; setze PORTA6 (/CS1) wieder auf HIGH

rdEnd:

ret

```

In r17 steht nunmehr das rückgelesene Daten-Byte des Display-RAMs zur weiteren Bearbeitung zur Verfügung. Vor der Zurück-Schreibung auf das Display-RAM muß die X-Adresse neu eingeschrieben werden, da nach jedem Zugriff (Takt) auf das Display-RAM dessen X-Adresse intern automatisch inkrementiert wird.

Der Test sollte mit einem Pixel-Muster erfolgen, wie unter UP GLCD\_clr erläutert.

#### 6.7.1 Test

Auch dieser Test mit den JTAGICEmkII verlief zunächst <u>nicht</u> positiv, weil noch einige Programmfehler (rot markiert) vorhanden waren. Die Programmfehler waren durch Kopieren die gleichen, wie unter <u>6.5</u>., so daß die Korrektur analog erfolgen muß.

#### Korrektur:

```

GLCD_read:

| Giltigkeit r13 ungeprüft, da im UP GLCD_SetX |

| Idi r16, 0b00111111 | ; 63 | ; prüfen, ob AdressWertX > 63 |

| brcc rd1 | ; AdrWertX <=63 | ; |

| Idi r16, 0b01111111 | ; 127 | ; prüfen, ob AdressWertX > 127 |

| brcc rd2 | ; 63 < AdrWert > 127 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64 | ; 64

```

Das UP BusyClread1 kann hier nicht verwendet werden, weil dieses ausschließlich für den Befehl "Status lesen" gedacht ist (Kriterium Test BusyFlag).

Das kann jedoch modifiziert werden in:

```

DatClread:

; E -> Taktimpuls HIGH

sbi PORTA, 2

; Impulsanfang, Impulsbreite >500ns

; pro Takt 62,5ns bei fT= 16 MHz

nop

nop

nop

nop

; nach 320ns liegen die gelesenen Daten

nop

; auf dem Datenbus vor

in r17, PIND ; akt. PIND-Daten sichern, auch noch nach E-LOW

nop

cbi PORTA, 2 ; E -> LOW, Impulsende

nop

; für mind. 500ns LOW

nop

nop

ret

```

Nach diesen Korrekturen funktionierte das Programm soweit erst einmal, d.h. in r17 konnte mit einer zufälligen X-/P-Adressierung der zurück gelesene Inhalt des betreffenden Display-RAMs nachgewiesen werden. Die zufällige Adressierung ergab sich bei X = 80H und P = 0 beim Step-Betrieb des JTAGICEmkII durch die Inhalte von r13 und r12 nach dem Start. Da der Inhalt "E1" (Hex) bedingt durch die Ausschaltung der Pixel-Löschung (siehe <u>6.3. GLCD\_clr</u>) jedoch auf alle Adressen zutrifft, ist das noch <u>kein</u> endgültiger Beweis einer korrekten Adressierung.

#### 6.8. UP GLCD write

Auch das UP GLCD\_write ist wichtig für Pixel-Manipulationen der/des GLCD-RAMs. Wie auch schon beim UP GLCD\_read sind vorher die betreffenden Adressen – X- und Page-Adresse – an die GLCD-Chips zu senden. Bei aufeinander folgenden X-Adressen braucht man das durch die automatische Inkrement-Funktion der X-Adresse zwar nur im Ausnahmefall des Übergangs von einem Chip auf den nächsten tun, aber trotzdem ist dadurch die Implementation externer Adresszähler notwendig. Für die Page-Adresse gibt es keine interne Inkrement-Funktion, so daß hier sowie so ein Adresszähler in Form eines Page-Zählers notwendig ist. Die eigentliche Y-Adresse ist dann innerhalb der betreffenden Page-Adresse verfügbar.

Diese Betrachtungen treffen genau so auch auf das UP GLCD\_read zu.

Durch die Page-Adressierung kann bei der Verwendung des UP GLCD\_write auch auf mehrere, maximal 8 Pixel untereinander gleichzeitig zugegriffen werden, ohne jedes Mal neu adressieren zu müssen. Das ist insbesondere bei der Erzeugung senkrechter Linien von Vorteil. Entsprechende Algorithmen müssen herausfinden, wo sich das betreffende Linienstück befindet – an Anfang, in der Mitte oder an Ende der Linie. Je nach dem werden dann über Masken-Operationen die betreffenden Bits = Pixel im Datenbyte = Page gesetzt oder auch nicht.

Das UP GLCD\_write erwartet das an die vorher definierte X- und Page-Adresse zu schreibende Byte im Register r16.

```

GLCD_write: push r16

; Datenbyte sichern

ldi r16, 0b00111111 ;63

; prüfen, ob AdressWertX > 63

sub r16, r13

brcc wr1

; AdrWertX <=63

ldi r16, 0b01111111 ; 127

sub r16, r13

; prüfen, ob AdressWertX > 127

; 63 < AdrWert > 127

brcc wr2

ldi R16, 0b11100001 ;/CS0 -/CS2 deaktiviert -

out PORTA, r16

; R/W = LOW, RS = HIGH (Daten)

pop r16

; DatenByte zurück

out PORTD, r16

ldi r16, 0b11111111

; PORTD auf Ausgang

out DDRD, r16

; damit liegt an PORTD das DatenByte an

cbi PORTA, 7

; setze PORTA7 (/CS2) auf LOW

; Übertragen auf Chip3

rcall Comm3on

```

```

rcall Comm3off

rjmp Write_end

ldi R16, 0b11100001 ;/CS0 -/CS2 deaktiviert -

wr1:

out PORTA, r16

; R/W = LOW, RS = HIGH (Daten)

; DatenByte zurück

pop r16

out PORTD, r16

ldi r16, 0b11111111 ; PORTD auf Ausgang

out DDRD, r16

; damit liegt an PORTD das DatenByte an

; setze PORTA5 (/CS0) auf LOW

cbi PORTA, 5

; Übertragen auf Chip1

rcall Commlon

rcall Commloff

rjmp Write_end

wr2:

ldi R16, 0b11100001 ;/CS0-/CS2 deaktiviert-

; R/W = LOW, RS = HIGH (Daten)

out PORTA, r16

; DatenByte zurück

pop r16

out PORTD, r16

ldi r16, 0b11111111

; PORTD auf Ausgang

; damit liegt an PORTD das DatenByte an

out DDRD, r16

; setze PORTA6 (/CS1) auf LOW

cbi PORTA, 6

; Übertragen auf Chip2

rcall Comm2on

rcall Comm2off

Write_end:

ret

```

Da hier die Parameter-Übergabe in r16 erfolgen soll, muß dieser Wert zunächst auf dem Stack gesichert werden, da die Chip-Auswahl ebenfalls dieses UPR benutzt.

Zur Übertragung auf die drei GLCD-Chips wird der umfangreiche UP-Satz CommXon /

commxoff benutzt, welcher in jedem Fall die Bereitschaft der Chips neue Daten zu empfangen berücksichtigt. Ggf. könnte das noch vereinfacht werden.

#### 6.8.1 Test

Zur besseren Übersicht wurde der Test mit gelöschtem Display (clr r16 ; alle Pixel aus – in GLCD\_clr) und separat vorgegebener Adresse vorgenommen:

```

ldi r16, 0b00101010 ; 42

mov r13, r16 ; damit X-Adresse "42" gesichert (1.Chip)

ldi r16, 0b00000011 ; 3

mov r12, r16 ; mit Page-Adresse "3" - etwa in Display-Mitte

ldi r16, 0b10101010 ; DatenByte (kleine punktierte senkrechte Linie)

rcall GLCD_write

```

Ein erster Test ergab, daß zwar eine senkrechte punktierte Linie gezeichnet wird, aber nicht an der programmierten Stelle:

$$X = 42, Page = 3$$

Das ist auch klar, weil zwar die Adress-Parameter übergeben, aber nicht das UP GLCD\_SetX und GLCD\_SetP aufgerufen wurden.

## Korrektur bzw. Ergänzung

ldi r16, 0b00101010 ; 42

; damit X-Adresse "42" gesichert (2.Chip) mov r13, r16